Sigasi develops an integrated development environment (IDE) called Sigasi Visual HDL, that makes chip designers more productive. Our IDE, based on Visual Studio Code (VS Code), is focused on VHDL and SystemVerilog, the two most common hardware design languages.

Sigasi Visual HDL provides the digital designer with all the facilities that are typically reserved for software developers, such as syntax checking, project management, refactoring, and autocompletion. Our tools can generate diagrams that help to analyze e.g. code structure using Sprotty .

public boolean canApply(Applicant applicant) {

var degrees = Set.of("Computer Science", "Informatics", "ICT");

return (applicant.isBachelor() || applicant.isMaster()) &&

degrees.contains(applicant.getDegree());

}

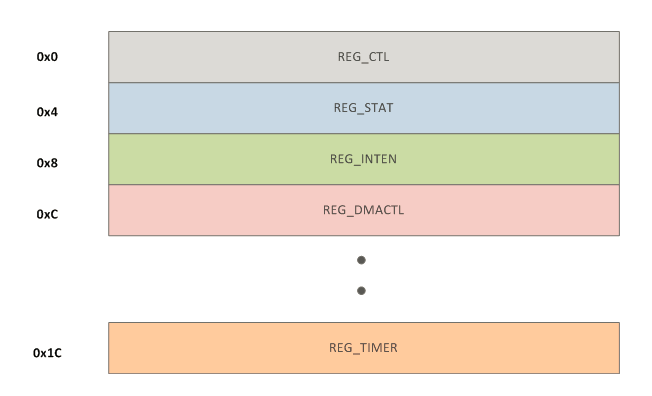

Missing from our diagrams is a UVM Register Layout View. This view should help engineers writing hardware verification code using the Universal Verification Methodology (UVM) to gain insight into the register blocks in their codebase.

You will join Sigasi’s code engineering team and participate in actual product development. You’ll be part of the daily scrum. Your code will be a first-class citizen, go through the standard review cycle, and eventually have a tangible impact on our product.

This internship takes place for at least 8 weeks in 2025, at the Sigasi office, near the fascinating city center of Ghent, Belgium. For more information about this internship proposal, e-mail careers@sigasi.com.

See also

- Data Mining Diagnostic Information (internships)

- Integrate Simulators in Sigasi Online (internships)

- WaveDrom Documentation Generation (internships)

- How to set up the UVM Library in Sigasi Visual HDL (knowledge)

- Running UVM tests in VUnit (blog post)