Sigasi provides powerful autocompletion capabilities. This means that the tool can help you complete identifiers and constructs as you are working on the code. Like other tools, it provides syntax-based autocompletion depending on the HDL language you’re using. However, it goes much further: it can also provide autocompletion based on the design context because it knows everything that has been declared in the design.

Autocompletion interface

Autocompletion can come from different sources, as discussed in the following sections. However, the user interface to initiate it is always the same. Sigasi will suggest appropriate autocompletion options at any point as you enter code.

You can also trigger autocompletion suggestions by first placing your cursor where you want to autocomplete and then pressing .

Based on the design context

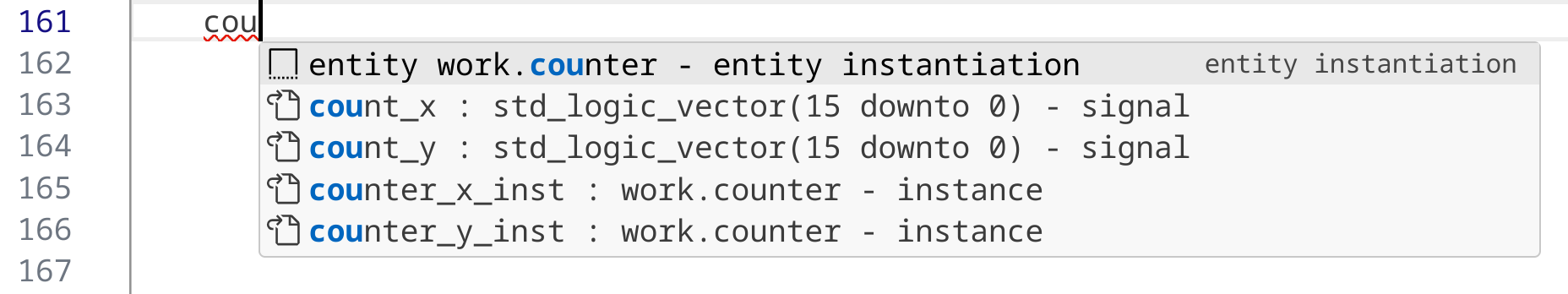

Sigasi uses its knowledge of designs to provide intelligent autocompletion that boosts your productivity tremendously.

The tool understands the current context, which identifiers are visible, and which constructs are legal at any given point in the code. As you start typing and ask for autocompletion, it will suggest appropriate identifiers as autocompletion candidates.

Sigasi provides autocomplete suggestions for:

- component declarations

- component instantiations

- entity instantiations

- module instantiations

- case statements (based on variables/signals with an enumeration type)

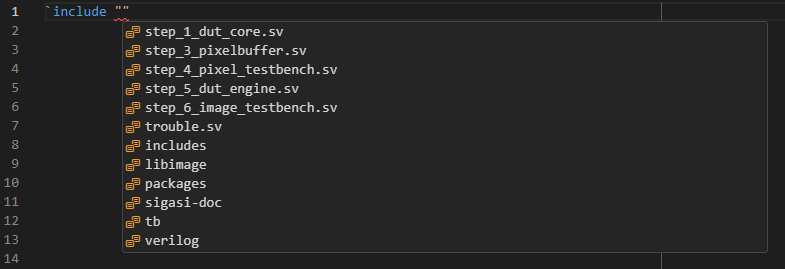

- SystemVerilog preprocessor/macro directives, e.g.,

`defineor`ifndef - SystemVerilog include paths (

`include ""): triggering autocomplete between the double quotes will present a list of files and folders. If you select a folder, trigger autocomplete again to get completions in this folder.

Based on templates

Sigasi can help you declare HDL constructs, using autocomplete based on templates. Sigasi comes preconfigured with templates for all common declarations and statements. For VHDL, this includes:

- function, procedure

- process

- type: enum, file, range, array, record

- signal, constant, variable

- component

- entity

- architecture

- entity/architecture pair

- package/package body pair

- and much more

Some autocompletions are templates that require further user input. In such a case, the editor window will go into a special template editing mode after performing an autocomplete. Use TAB to go through the items that have to be modified or completed. When done, press ENTER to return to normal editing mode. The cursor will be placed at an appropriate position to continue working.

User-defined code snippets

VS Code supports user-defined code snippets, as explained here . To add snippets yourself, follow the steps below.

- Open the Command Palette ( ) and type Snippets.

- Select Snippets: Configure User Snippets.

- Type vhdl or systemverilog to open the corresponding JSON file where you can add your snippet. See the examples below.

SystemVerilog snippet example

{

"always posedge clk": {

"prefix": "always",

"body": [

"always @(posedge ${1:clk}) begin",

"\t$0",

"end"

],

"description": "Insert an always block with posedge clock"

}

}

VHDL snippet example

{

"package declaration": {

"prefix": "package",

"body": [

"package ${1:name} is",

"\t$0",

"end package $1;"

],

"description": "Insert package declaration"

}

}

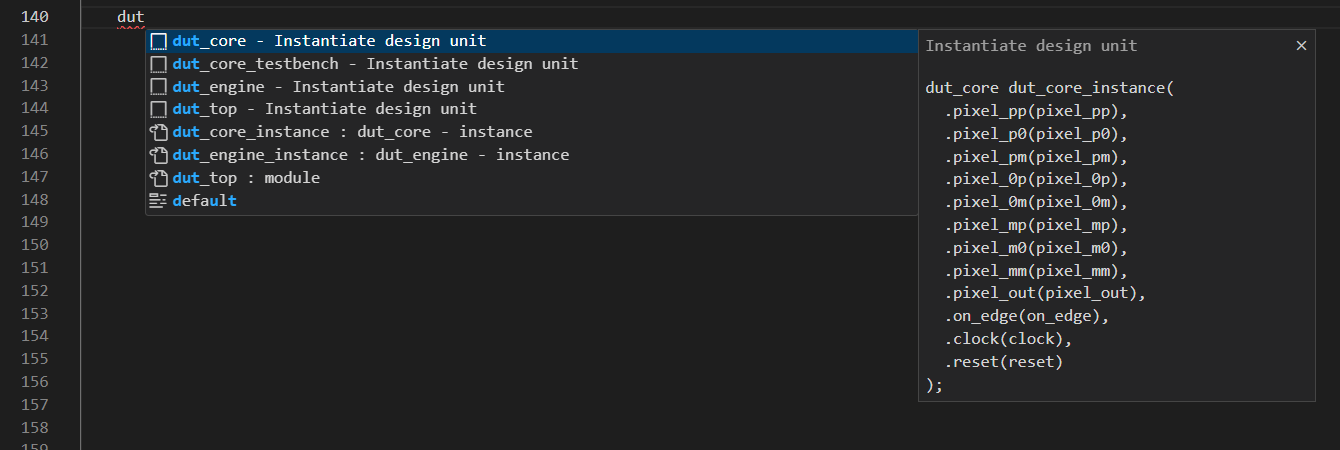

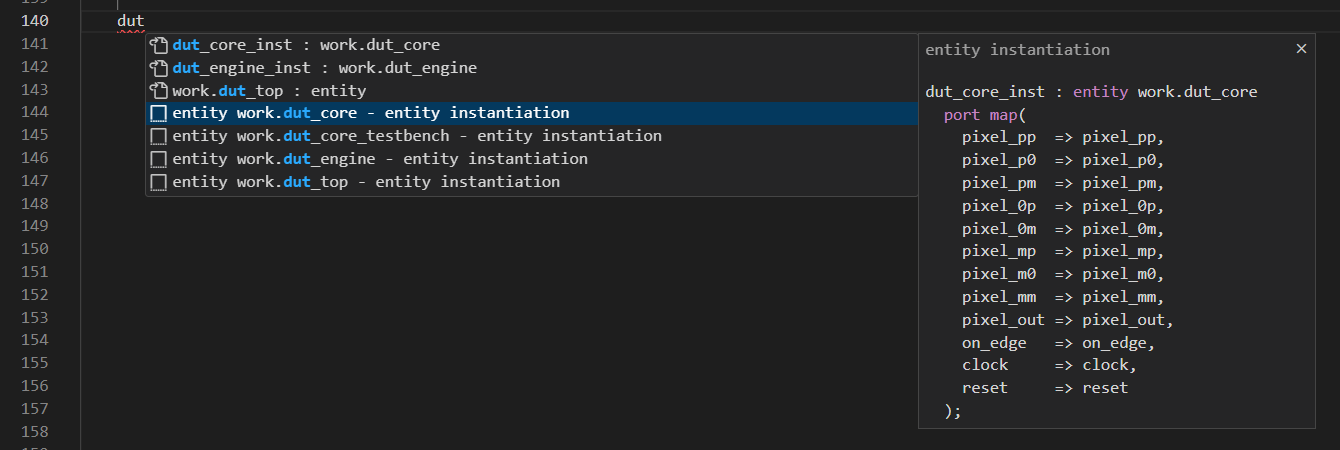

Instantiating a design unit

Note: In other tools, this feature may be known as paste as instantiation or port translation.

Sigasi knows all design units (entities, components, and modules) in a design and their ports and parameters or generic interfaces, and can therefore automate much of the instantiation process. At the point in the code where you normally enter a design unit’s name, use autocompletion instead to suggest a list of possible design units. Upon selection, the tool will complete the instantiation with a generic or parameter list, and a port list with named associations. As an initial suggestion, each actual parameter will have the same name as its formal parameter. Of course, the actual parameter names need to be reviewed and edited by the user. Therefore, the editor will go into template editing mode after the autocompletion.

Note that design units will only be shown if they are visible in the current scope.

Inserting an include file

Making a typo in the filename of an `include causes swarms of errors. To prevent this, you can simply press

between the double quotation marks of an include directive. You’ll be presented with all the files reachable from

your current include path.

Declaring a component

If you want to create an instantiation based on a component (as opposed to a direct entity instantiation), you need to associate an entity with a component. Sigasi can automatically declare a component for an existing entity. In the place where you would normally enter the component name, use autocomplete instead to show the list of available entities. Upon selection, the tool will automatically complete the component declaration.

Autocomplete suggestions automatically appear and are updated as you type.

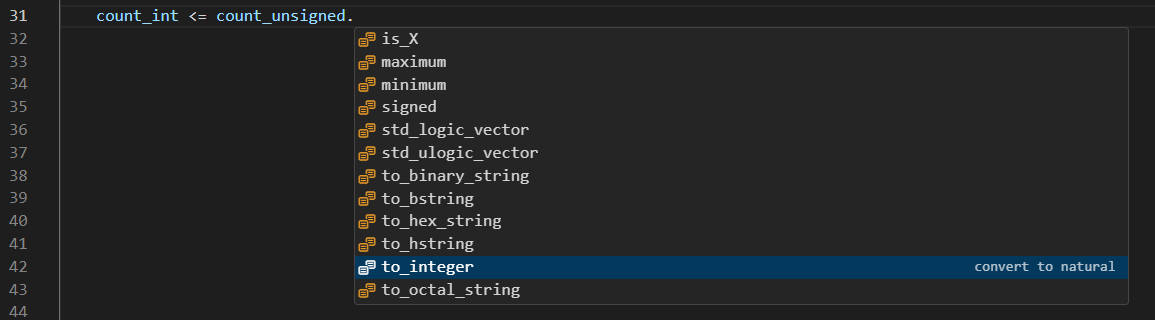

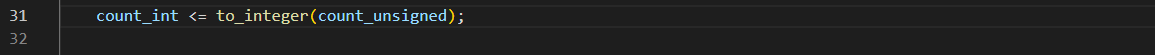

Type conversion

In VHDL design, you need to do a lot of type conversions, and Sigasi’s

autocomplete functionality can help you here. Put a period (.)

after the element you want to convert and the autocomplete suggestions

will appear with descriptions like convert type.

Once you select the desired conversion function, Sigasi will insert the code.