Sigasi extension supports syntax- and semantic code highlighting, sometimes called syntax- and semantic coloring, even though it can also apply styling (cursive, bold, etc).

- Syntax highlighting: colors and styles code according to lexical classification (such as keyword or string). Always present, event for HDL files outside of projects.

- Semantic highlighting: colors and styles code according to meaning (different colors for constants and signals). Only activate for HDL files in projects.

Note that some VS Code themes might not support semantic highlighting. If you appear to be missing this feature, ensure you’re using one of the default VS Code themes.

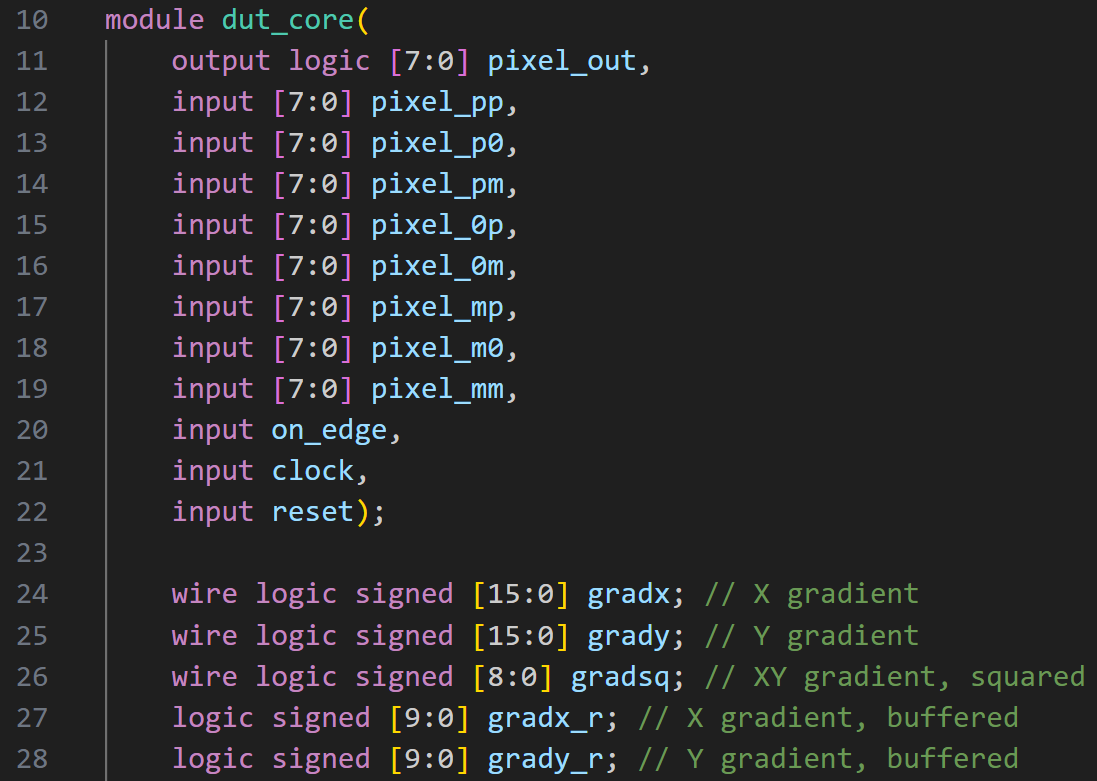

- In themes that support semantic highlighting, you’ll see that names like those of a

port,signal, ortypeare a different color (light blue) from language keywords (purple). - In themes that do not support semantic highlighting, names like those of a

port,signal, ortypewill have the default text color (white).

Customizing your setup

Semantic highlighting colors—as well as font style—can be customized to your wishes as follows:

- Open VS Code Settings:

Navigate to and search for

editor.semanticTokenColorCustomizations - Edit or add your rules: Modify the existing rules or add new ones based on the semantic tokens below. You can use the examples provided below as a starting point.

- Save your changes: Once you’ve made your customizations, save the settings file. The new semantic coloring will be applied immediately.

Example settings

Below is an example of a semantic coloring configuration.

Dark theme

{

"editor.semanticTokenColorCustomizations": {

"[Name of theme 1]": {

"enabled": true,

"rules": {

// Verilog and SystemVerilog

"sigasiCoverageGroup:systemverilog": "#4EC9B0",

"sigasiCoveragePoint:systemverilog": "#71CBFC",

"sigasiCoverageCross:systemverilog": "#49B8F4",

"sigasiCoverageBin:systemverilog": "#71CBFC",

"sigasiNamedSequence:systemverilog": "#D0D092",

"sigasiNamedProperty:systemverilog": "#C5C57B",

"sigasiClockingBlock:systemverilog": "#49B8F4",

"sigasiConstraint:systemverilog": "#4FC1FF",

"sigasiRandsequenceProduction:systemverilog": "#D0D092",

"sigasiAssertion:systemverilog": "#2ABEA1",

// VHDL

"sigasiPort:vhdl": "#3f9acc",

"sigasiConditionalProcessingVariable:vhdl": "#457dab",

"sigasiSignal:vhdl": "#4FC1FF",

"sigasiSubprogramParameterVariable:vhdl": "#9CDCFE",

"sigasiSubprogramParameterSignal:vhdl": "#4FC1FF",

"sigasiSubprogramParameterConstant:vhdl": "#E5C07B",

"sigasiConstant:vhdl": "#E5C07B",

"sigasiAttribute:vhdl": "#eacd95",

"sigasiGenericConstant:vhdl": {

"italic": true,

"foreground": "#E5C07B"

},

"sigasiGenericType:vhdl": {

"italic": true,

"foreground": "#E5C07B"

},

"sigasiGenericSubprogram:vhdl": {

"italic": true,

"foreground": "#DCDCAA"

}

}

}

}

}

Light theme

{

"editor.semanticTokenColorCustomizations": {

"[Name of theme 1]": {

"enabled": true,

"rules": {

// Verilog and SystemVerilog

"sigasiCoverageGroup:systemverilog": "#4EC9B0",

"sigasiCoveragePoint:systemverilog": "#00139F",

"sigasiCoverageCross:systemverilog": "#0119CE",

"sigasiCoverageBin:systemverilog": "#00139F",

"sigasiNamedSequence:systemverilog": "#806733",

"sigasiNamedProperty:systemverilog": "#857045",

"sigasiClockingBlock:systemverilog": "#0119CE",

"sigasiConstraint:systemverilog": "#0070C1",

"sigasiRandsequenceProduction:systemverilog": "#806733",

"sigasiAssertion:systemverilog": "#448DA1",

// VHDL

"sigasiPort:vhdl": "#004e87",

"sigasiConditionalProcessingVariable:vhdl": "#4d4dff",

"sigasiSignal:vhdl": "#0070C1",

"sigasiSubprogramParameterVariable:vhdl": "#001080",

"sigasiSubprogramParameterSignal:vhdl": "#0070C1",

"sigasiSubprogramParameterConstant:vhdl": "#b78b12",

"sigasiConstant:vhdl": "#b78b12",

"sigasiAttribute:vhdl": "#926f0e",

"sigasiGenericConstant:vhdl": {

"italic": true,

"foreground": "#b78b12"

},

"sigasiGenericType:vhdl": {

"italic": true,

"foreground": "#b78b12"

},

"sigasiGenericSubprogram:vhdl": {

"italic": true,

"foreground": "#795E26"

}

}

}

}

}

Token descriptions

The token keywords below are used to configure the styling of SystemVerilog and VHDL constructs.

| Token | Construct |

|---|---|

sigasiCoverageGroup | A SystemVerilog coverage group |

sigasiCoveragePoint | A SystemVerilog coverage point |

sigasiCoverageCross | A SystemVerilog coverage cross |

sigasiCoverageBin | A SystemVerilog coverage bin |

sigasiNamedSequence | A SystemVerilog named sequence |

sigasiNamedProperty | A SystemVerilog named property |

sigasiClockingBlock | A SystemVerilog clocking block |

sigasiConstraint | A SystemVerilog constraint |

sigasiRandsequenceProduction | A SystemVerilog randsequence production |

sigasiAssertion | A SystemVerilog assertion |

sigasiPort | A VHDL port |

sigasiPort.sigasiInputPort | A VHDL input port |

sigasiPort.sigasiOutputPort | A VHDL output port |

sigasiPort.sigasiInoutPort | A VHDL inout port |

sigasiConditionalProcessingVariable | A VHDL conditional processing variable |

sigasiSignal | A VHDL signal |

sigasiSubprogramParameterVariable | A VHDL variable parameter of a task or function |

sigasiSubprogramParameterSignal | A VHDL signal parameter of a task or function |

sigasiSubprogramParameterConstant | A VHDL constant parameter of a task or function |

sigasiConstant | A VHDL constant or enumeration literal |

sigasiAttribute | A VHDL attribute |

sigasiGenericConstant | A VHDL generic constant value |

sigasiGenericType | A VHDL generic type declaration |

sigasiGenericSubprogram | A VHDL generic function or task |