In VHDL, many constructs are split between definition and implementation. For example, a package and its corresponding package body or a component and its corresponding entity.

Navigating between these is often done through text searches that also find false positives. Sigasi understands your entire design, so you can simply hover over the name of a definition and click Find All Implementations. To go from an implementation back to the definition, use Go to definition.

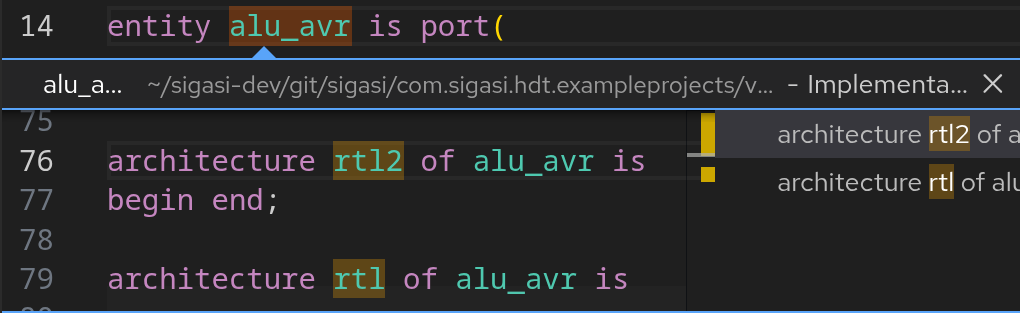

To immediately jump to the only implementation or show an inline peek of all existing implementations, right-click an identifier and select Go to Implementations.

If Go to Implementations on an identifier points to itself, VS Code can perform an alternative action. This can be customized via the

setting.editor.gotoLocation.alternativeImplementationCommand

Supported constructs

| Definition | Implementation |

|---|---|

| Entity | Architecture |

| Package | Package body |

| Package constant | Package body constant |

| Subprogram prototype | Subprogram body |

| Protected type | Protected type body |

Verilog

In Verilog, there are no split definition like in VHDL. However, there are extern methods and their body. To navigate between these, you can use Go to definition and Go to declaration.