Now that you have a working setup, let’s put Sigasi through its paces. We’ll start by creating a “Hello World” project to showcase the basics of project creation.

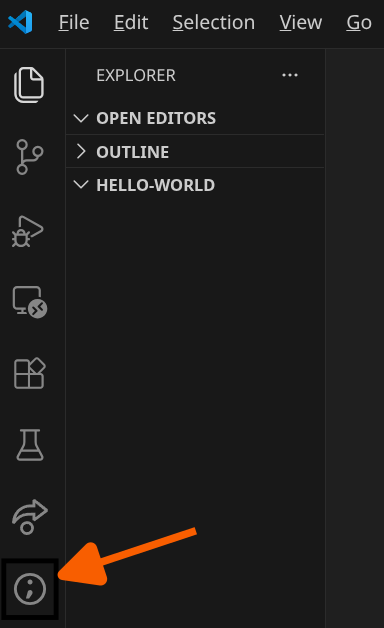

First, create a folder called hello-world in a location that suits you. Now, start VS Code and open the hello-world folder ().

You should see an empty VS Code workspace focused on the Explorer Activity. The real action happens in the Sigasi Activity, indicated by the Sigasi logo,

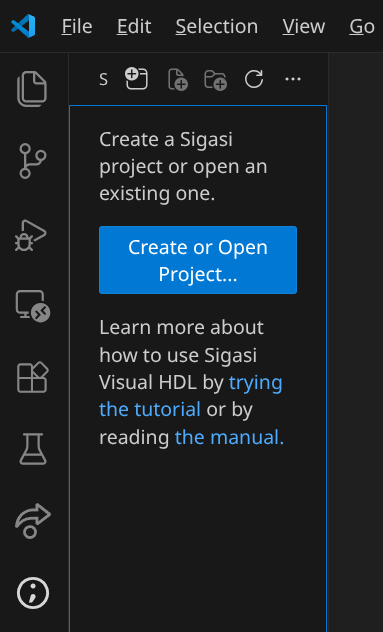

Here you are prompted to create or open a project. Click the Create or Open a Project button to initialize the project in the hello-world folder.

If you switch to the Explorer, you will find that the hello-world folder now contains a .project file, a .library_mapping.xml file, and a .settings folder. This is where Sigasi stores project metadata. In general, when you open a folder containing a .project file, Sigasi will automatically initialize.

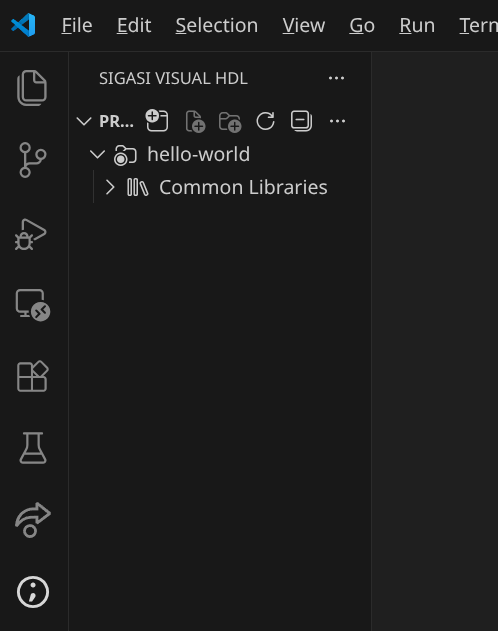

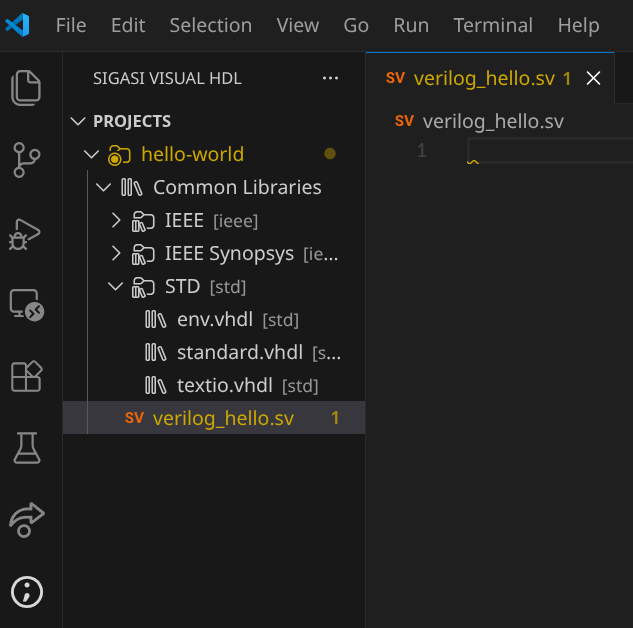

The hello-world project is now shown in the Projects View. Currently, it is empty except for the Common Libraries folder, which contains standard VHDL libraries such as standard.vhdl and textio.vhdl. These files are virtual and do not exist on your physical disk; they are provided so you can consult standard definitions when needed. Users working exclusively with Verilog can safely ignore this folder.

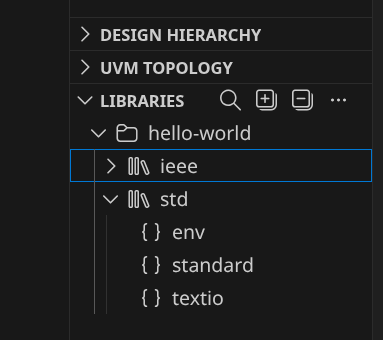

What else is there? There are also the Design Hierarchy, UVM Topology, and Libraries views. Let’s have a quick look at the Libraries View.

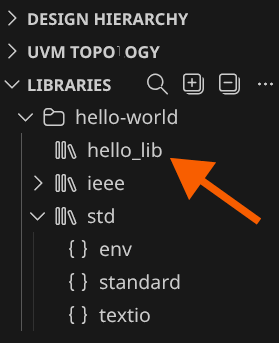

At the moment, two libraries are listed: ieee and std. These contain the standard VHDL files. As you develop your project, you will populate this view with your own libraries and design units.

Now, let’s add some content. We’ll create one SystemVerilog file and one VHDL file to demonstrate the simplest use case. Right-click the hello-world node in the Projects View and select New File…. Name the file verilog_hello.sv. Because of the .sv extension, Sigasi recognizes it as a SystemVerilog file.

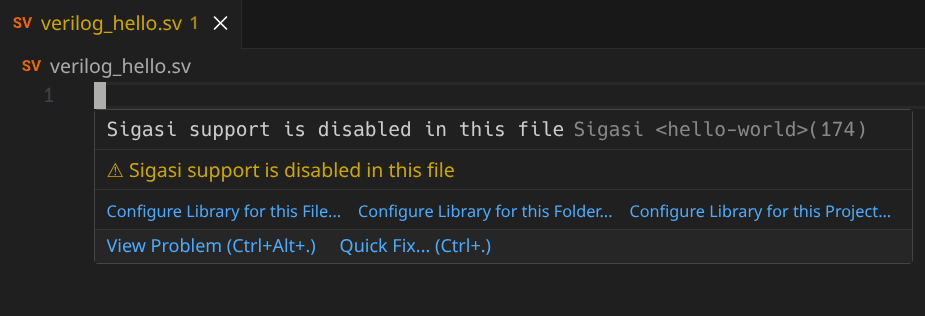

You will notice a small yellow squiggle at the top of the file. This is a warning from Sigasi. Hovering over the squiggle reveals a hint.

It says “Sigasi support is disabled in this file”, indicating that the file is not yet being analyzed. To enable full support, the file must be assigned to a library.

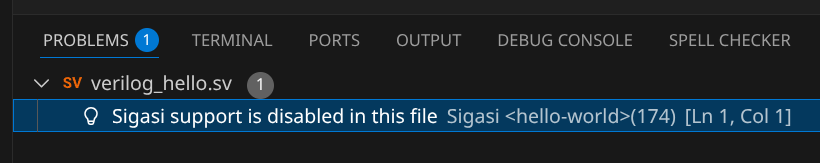

You can also inspect these warnings in the Problems View ().

To fix the problem, hover over the squiggle again and select Configure Library for this Project…. This allows you to set a default library for the entire project. Enter the library name hello_lib. The warning will disappear as Sigasi begins analyzing the file. Any new files added to the project will now be automatically assigned to hello_lib.

If you look at the Libraries View again, hello_lib will now be visible. The Libraries View only shows libraries that are currently in use.

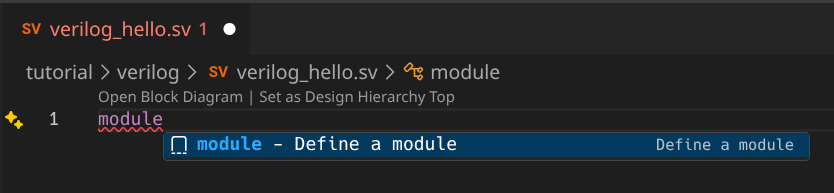

Next, let’s add a module declaration. Place your cursor in the editor and press

to open Content Assist. Start typing module and press Enter when the module template is selected. Sigasi will insert a module skeleton for you.

Note that Sigasi automatically names the module verilog_hello to match the filename. It also flags clk and rst as unused ports—a helpful linting feature we will explore later.

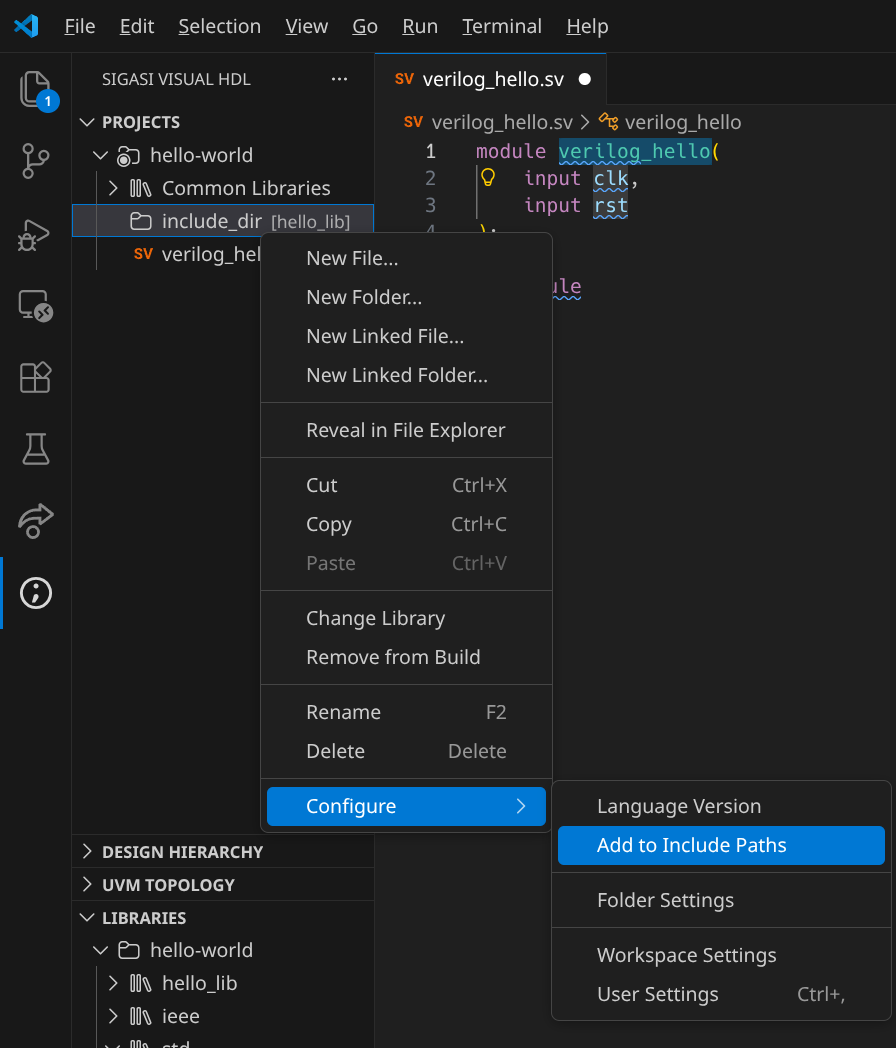

To properly set up Verilog projects, you often need to configure include paths. First, create a folder called include_dir by right-clicking the project node and selecting New Folder…. To tell Sigasi to use this folder for includes, right-click include_dir and select .

Now, any files created in include_dir can be included in your Verilog files. For example, if you add my_include_file.svh to include_dir, typing `include "my_include_file.svh" will be correctly recognized.

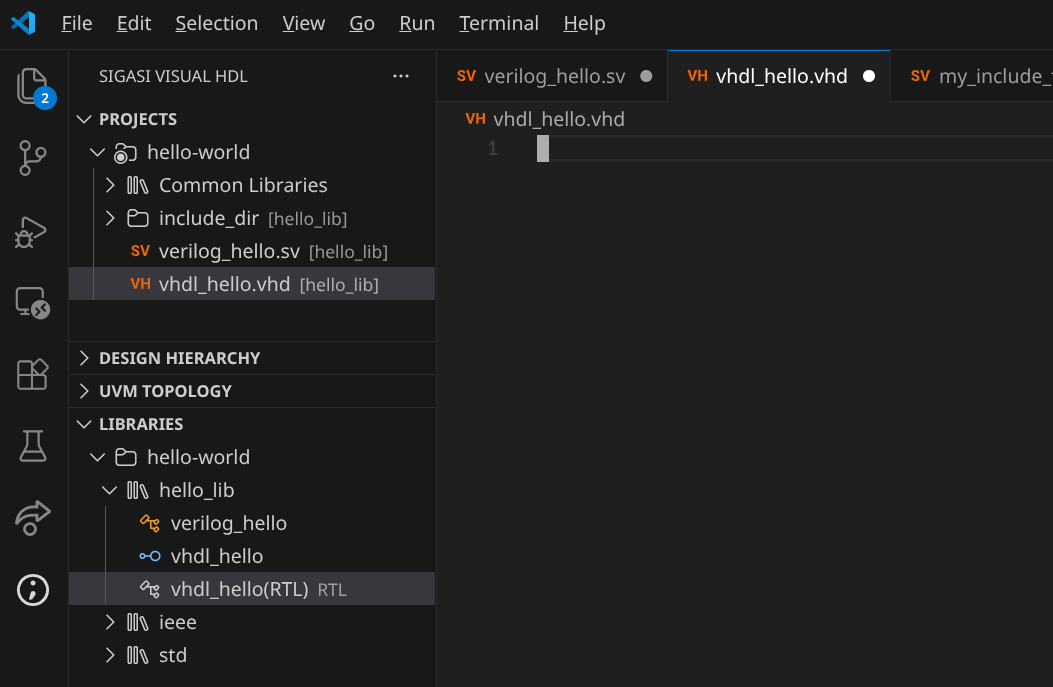

Finally, let’s create a VHDL file. Right-click hello-world in the Projects View and select New File…. Name it vhdl_hello.vhd.

Notice that vhdl_hello.vhd is already mapped to hello_lib because we previously assigned the entire project to that library.

To add content, place your cursor in the empty file, press

, and type entity/arch.... Select the entity/architecture pair template. Just like with SystemVerilog, Sigasi creates the boilerplate for you, naming the entity vhdl_hello.

When you are ready to share your hello-world project with colleagues, remember to check the project metadata into your version control system. For Sigasi, you should include the .project and .library_mapping.xml files, as well as the .settings folder.