The primary purpose of hardware description languages (HDLs) is to define designs for hardware synthesis and implementation. However, both VHDL and SystemVerilog include features specifically for verification. You can write testbenches to provide stimulus to DUTs and validate that their outputs match expected values. Because this verification code is typically non-synthesizable, it must be handled differently than RTL code.

Avoid using verification-specific language features in synthesizable designs. To improve synthesis Quality of Results (QoR), designs must follow strict coding rules. However, because these rules only apply to synthesizable logic, there is no need to enforce them in verification code.

To provide better feedback, Sigasi identifies which parts of your code are intended for synthesis and applies relevant rules. It classifies design units into one of the following description styles:

- Testbench: A top-level verification module.

- Behavioral: Design units intended for verification purposes (e.g., bus functional models).

- RTL: Design units that are part of the actual design intended for synthesis.

Sigasi allows you to specify different rule severities for RTL and non-RTL code. You can also disable specific checks for either style by setting the severity to ignore.

VHDL

In VHDL, Sigasi detects the description style for every architecture, either by identifying verification-specific constructs or by analyzing architecture names.

Detection via constructs

This is the default method. Sigasi classifies an architecture as:

- Testbench, if the corresponding entity has no ports.

- Behavioral, if it contains non-synthesizable processes (e.g., processes with no sensitivity list or multiple

waitstatements) or if it uses thestd.textiopackage or declares file types. - RTL, in all other cases.

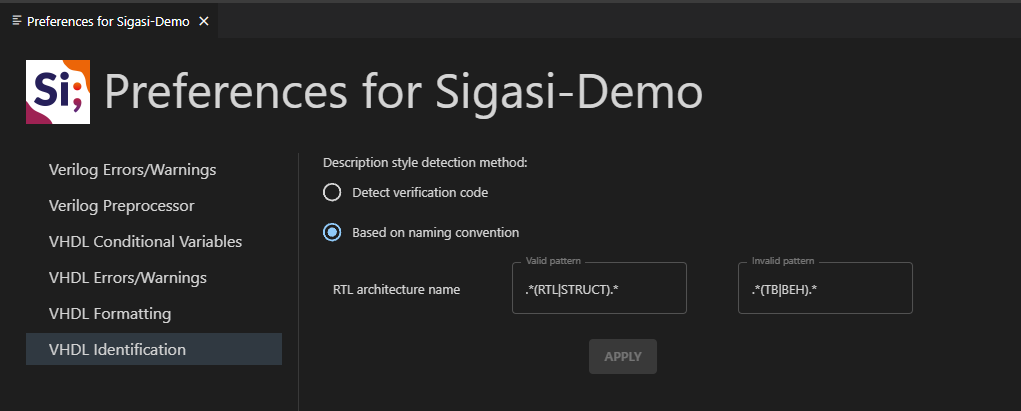

Detection via naming patterns

If you require more fine-grained control, you can classify styles based on architecture names by specifying regex patterns in the settings.

- RTL, if the name matches the valid pattern and does not match the invalid pattern.

- Testbench, if the corresponding entity has no ports.

- Behavioral, in all other cases.

SystemVerilog and Verilog

Currently, SystemVerilog and Verilog rules do not utilize description styles; therefore, style detection is not performed for these languages.