Boost Your Productivity with Sigasi Visual HDL

We’re excited to introduce a new series of short screencasts that show how Sigasi Visual HDL helps FPGA and ASIC engineers work more efficiently—whether you’re writing code from scratch, reusing existing IP, or integrating AI-generated designs.

AI in RTL Development

AI assistants and agents can generate RTL fast. But in chip design, generated code still has to be reviewed, validated, and understood in full project context before it can move forward.

Sigasi at Chip Development Symposium

After our second conference of the year in the USA, our team is heading for Europe, where we will be present at the Bavarian Chip Design Center (BCDC) Symposium: “Artificial Intelligence in Chip Design.”

Sigasi Visual HDL 2026.1

This release strengthens what matters most in professional FPGA and ASIC development: fast, deterministic, project-aware feedback — even as designs grow larger and workflows evolve.

Survey Results

As Sigasi turns 18, we asked our users a simple question: How are we doing — and what should we improve next? 100’s of respondents took the time to give structured feedback. What we learned reinforces the direction we’re taking.

Sigasi at GOMACTech 2026

After our first conference of the year in India, our team is now heading for New Orleans where we will be present at GOMACTech 2026: “Beyond the Noise” in Government Microelectronics.

Sigasi, your first line of defense

A recent GPTZero investigation should make every engineer pause. They scanned 4,841 accepted NeurIPS 2025 papers and reported 100+ confirmed hallucinated citations spread across 50+ papers; issues that slipped past “3+ reviewers” per paper.

AI in Chip Design - Webinar

Join us on March 24th for our first webinar on AI. You’ll learn how Sigasi’s approach allows you to safely integrate AI in Chip Design. A must watch for engineers that want to go faster by using AI but don’t want to take the risks associated with AI.

18th Birthday

Exactly 18 years ago today, our founders—Hendrik Eeckhaut, PhD in Computer Science Engineering, and Philippe Faes, freshly graduated at the time—launched Sigasi with a single mission: “to make chip design easier and faster”.

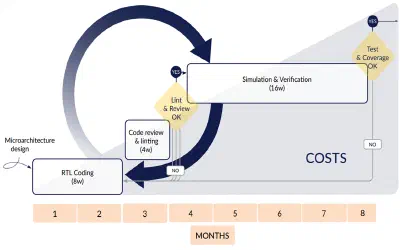

Done doesn't mean "correct"

If you’re managing chip projects, the hardest part isn’t writing/generating more RTL; it’s predicting verification + debug. This isn’t an “FPGA problem” or an “ASIC problem.” It’s a verification predictability problem.

The 7 Advantages for (E)CAD Managers

The success of an (E)CAD Manager is measured on predictable delivery and risk reduction. Tooling decisions directly impact productivity, code quality, onboarding speed, and ultimately time-to-market. That’s exactly where Sigasi Visual HDL makes the difference.

Verification is eating the schedule

The 2024 Wilson Research Group Functional Verification Trend Reports point to a harsh reality: design complexity is rising faster than verification capacity, and the industry is paying for it in escapes, respins, and delays.

12,000 Downloads and Counting

It took us more than one year to get to 10,000 downloads. In less than 2 months, 2,000 more downloads were done. Our mission to empower design and verification engineers to save time and costs for their team/company pays off.

Verification Frameworks - Webinar on demand

On January 28th we presented our first webinar in 2026, in which we showed how Sigasi’s shift-left approach saves you valuable time and money in verification. A must watch for design & verification engineers in both SystemVerilog and VHDL.