In A Nutshell

Everything You Need to Know About FSMs

Finite State Machines (FSMs) are an essential tool in a digital designers toolkit, especially when control flow, sequencing, and decision-making are involved. Whether you’re writing RTL code for FPGAs or crafting a control unit for a processor, FSMs play a central role in simplifying complex behaviors.

This article distills key insights from expert resources to give you a full-spectrum understanding of FSMs — from theory to VHDL implementation.

🧠 What Is an FSM?

An FSM is a computation model that can exist in exactly one state at a time, and transitions between states based on inputs and conditions. It’s ideal for modeling systems that respond to sequential inputs over time.

FSMs are classified into two main types:

1. Moore Machine

- Outputs depend only on the current state.

- Simpler timing, but may need more states.

2. Mealy Machine

- Outputs depend on current state and inputs.

- Typically requires fewer states, but can be more timing-sensitive.

✅ Use Moore when output timing needs to be predictable.

✅ Use Mealy when design compactness matters more.

🛠️ FSM Design Styles in VHDL

There are two dominant coding styles for FSMs in VHDL:

🔁 1. Single Process FSM

All logic (state transitions, registers, and outputs) are inside one clocked process. It’s easier for simple FSMs, but can get messy in complex systems.

📘 Source: VHDLwhiz – Finite State Machine

🔄 2. Multiple Process FSM (Recommended)

Typically split into 3 processes:

- Synchronous process for state register

- Combinational process for next state logic

- Combinational process for output logic

📘 Source: VHDLwhiz – N-process FSM

🧬 FSM Encoding: Binary vs One-Hot

🧮 Binary Encoding

- Minimum number of flip-flops (log₂(N) for N states).

- May produce complex combinational logic.

🔥 One-Hot Encoding

- One flip-flop per state; only one bit is ‘1’ at any time.

- Simple logic and faster transitions.

- Ideal for FPGAs, which have abundant flip-flops.

📘 Source: Sigasi – One-Hot FSM

🧪 Practical Example: Sequence Detector FSM

A great example is a Sequence Detector — a design that detects a specific bit pattern in a stream.

- Moore FSM delays output until entering the final state.

- Mealy FSM gives output immediately once the final input is received.

📘 Source: AllAboutFPGA – Sequence Detector

💣 Common Pitfalls in FSM Design

- ❌ Unintentional Latches: Forgetting default values in combinational processes.

- ❌ Improper Resets: Poor reset strategies cause simulation-synthesis mismatches.

- ❌ Inconsistent Output Timing: Mealy FSMs can glitch if not handled carefully.

✅ Always simulate thoroughly

✅ Use enumerated types

✅ Keep output logic isolated from state transitions

✅ Best Practices for FSM Design

- Use enumerated types for states

- Isolate logic into 3 processes

- Add default assignments in combinational logic

- Comment your state transitions

- Modularize FSMs for reuse

🧰 Sample FSM Skeleton in VHDL (3-Process)

type state_type is (IDLE, LOAD, PROCESS, DONE);

signal state, next_state: state_type;

-- 1. State register

process(clk, reset)

begin

if reset = '1' then

state <= IDLE;

elsif rising_edge(clk) then

state <= next_state;

end if;

end process;

-- 2. Next state logic

process(state, start, execution_complete)

begin

case state is

when IDLE =>

if start = '1' then

next_state <= LOAD;

else

next_state <= IDLE;

end if;

when LOAD =>

next_state <= EXECUTE;

when EXECUTE =>

if execution_complete = '1' then

next_state <= DONE;

else

next_state <= EXECUTE;

end if;

when DONE =>

next_state <= IDLE;

end case;

end process;

-- 3. Output logic

-- In this example 'output' is just a signal resembling some output logic

process(state)

begin

case state is

when IDLE => output <= '0';

when LOAD => output <= '0';

when EXECUTE => output <= '1';

when DONE => output <= '0';

end case;

end process;

🚀 Why FSMs Are Essential for RTL Engineers

FSMs are fundamental for:

✅ Communication protocols ✅ CPU control units ✅ Robotic control logic ✅ Protocol engines ✅ Traffic light controllers

By mastering FSMs, your HDL becomes easier to simulate, synthesize, and scale.

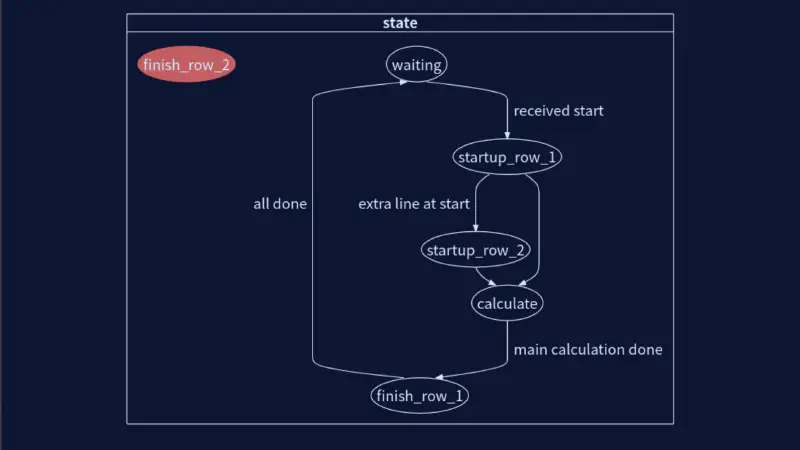

Want to see how Sigasi Visual HDL helps design better FSMs faster?

Mastering FSMs with Sigasi Visual HDL

FSMs play a central role in simplifying complex behaviors and it’s one of the most transferable skills across ASIC, FPGA, and SoC development. Sigasi visualizes FSMs in real-time while you write.

2025-07-03, last modified on 2025-07-04