Productivity cannot improve without speed. So we are proud to present the Sigasi Studio 4.5 release, where Sigasi Studio’s editor became a lot faster, as in up to 3 times faster. We also added HTML documentation, a lot of new lintings, and more.

Faster Editor

We have put a lot of effort in improving the speed of Sigasi Studio’s editor for Verilog, SystemVerilog and VHDL. We have redesigned Sigasi’s engine for the editor to run more tasks in the background. This prevents you from blocking the user interface, even when you are editing big source files. If you are working with UVM, the difference will be very noticeable. For projects with lots of `include files, Sigasi Studio is now even 3 times faster.

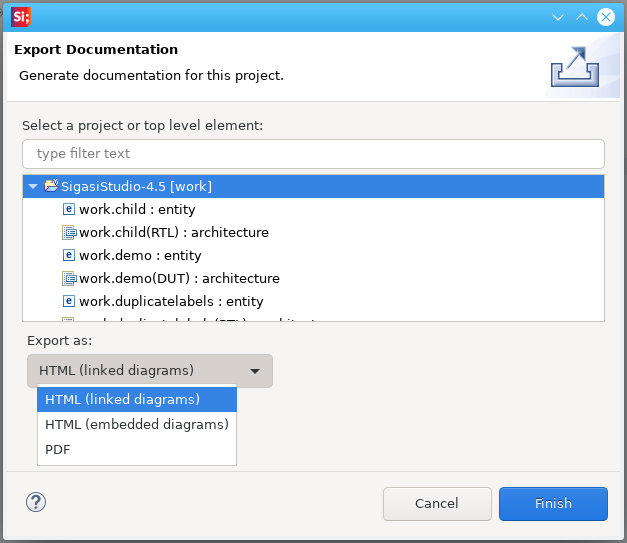

HTML documentation export

We implemented a new documentation engine in Sigasi Studio. This new engine produces HTML straight from your HDL sources. This is much faster and simpler than the previous DocBook based flow. The DocBook based flow was too complicated and too difficult to customize. The new HTML output is a lot easier to share and customize (for example with Microsoft Word).

Sigasi Studio offers two versions of html output:

- HTML with embedded diagrams: the result is saved in one self-contained html file. This file is very easy to share.

- HTML with linked diagrams: the diagram files are saved in separate files. This makes it easier to customize the documentation

More lintings

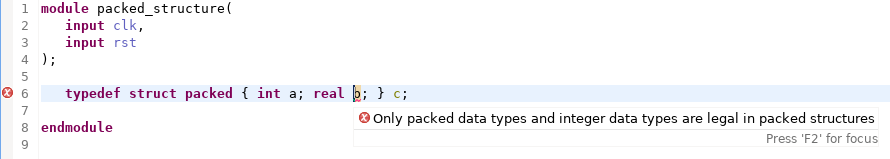

New (System)Verilog lintings:

- Check

packed struct,packed unionanduntagged union - Check for missing

caseitems in SystemVerilogcasestatements

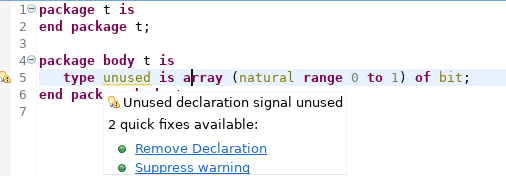

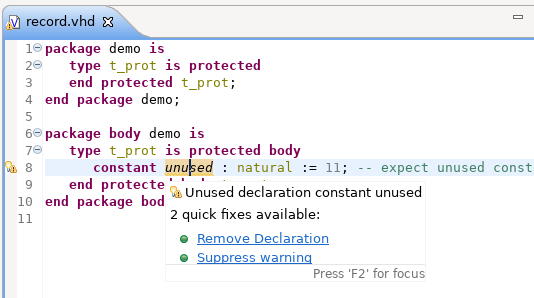

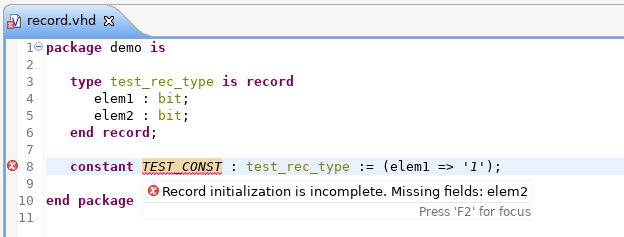

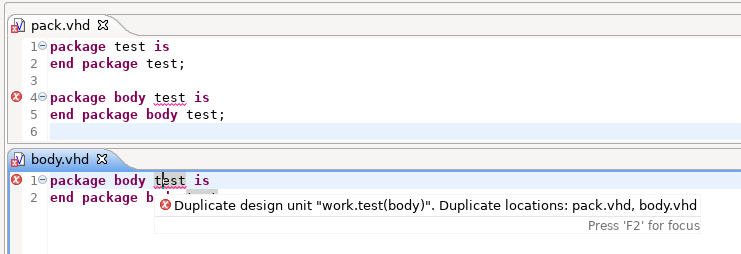

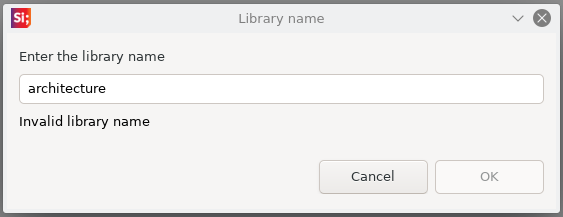

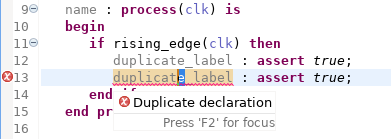

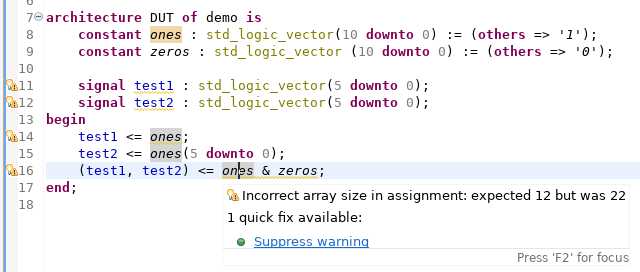

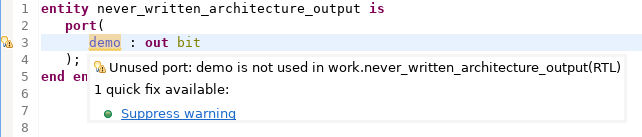

New VHDL lintings:

- Report unused declarations in

package body - Report unused declarations in

protectedtypes - Check that all fields are set in

recordinitializations - Check for duplicate

package bodydeclarations - Do not allow VHDL keywords as

libraryname - Check for duplicate labels in sequential statements

- Check vector width when assigning to aggregate

- Report for

output portsthat are never assigned

Split Editor View

The Split Editor has been enabled for VHDL and (System)Verilog editors.

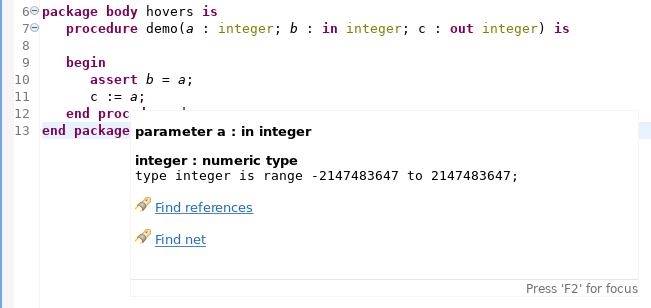

Other New and Noteworthy Changes

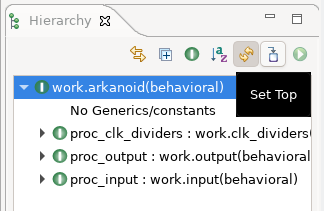

- Set Top Level now has an icon

- [Block Diagram] Support non-ANSI port declarations in (System)Verilog block diagrams

- [Block Diagram] Only show content of the active SystemVerilog editor in the block diagram, filter content of

`includefiles. - [VHDL] Improved outline for

recordfield assignments - [VHDL] Improved hover over

procedureparameters: show mode (in,out,inout) - [VHDL] The

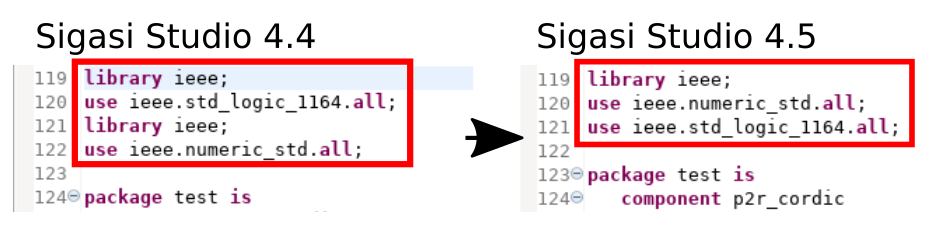

useclause quickfix now tries to reuse existinglibraryclauses instead of adding duplicates - Updated Xtext dependency to

2.18.0 - The stand-alone version of Sigasi Studio is now based on Eclipse 2019-06 (4.12). The plugin version works on Eclipse 4.7.3a and newer (unchanged)

- The default heap size in

sigasi.inihas been updated from1.5Gto3G. In case you want to adjust the heap size, follow these instructions.

Bugfixes

[Toolchains] Allow empty default parameters in the toolchain preference pages

[(System)Verilog] Comment folding in include files

[VHDL] Hover declarative items in protected types

[(System)Verilog] auto complete in Preprocessor property page

[(System)Verilog] allow empty content in the Preprocessor property page

[(System)Verilog] Reevaluate the Preprocessor property page when Undo is used.

[VUnit] Support linked resources in

run.py[(System)Verilog] No syntax error for anonymous nested sequential blocks

[VHDL] Net Search not showing load when net is used in

ifstatement with binary or unary expressions[VHDL] VHDL Formatting bug in indexed port map

[(System)Verilog] Out of Memory bug evaluating invalid preprocessor code

[(System)Verilog] Find references fails on

`includes[VHDL] Nicer hovers for record types

[Mixed] Unexpected errors on verilog module instantiations in VHDL code

[Mixed] A VHDL component declaration autocomplete of a Verilog module should use integer types for generics for parameters

[Other] CSV top level export does not always update when you set a new top level

A lot of other issues we could fix thanks to your Talkback reports

System requirements

- Sigasi Studio Standalone is supported on:

- Windows: Windows 10 (64 bit) or newer

- macOS 10.14 Mojave

- Linux: Red Hat Enterprise Linux RHEL 7.5 (64 bit) or newer

- More information on supported OSes can be found on the Eclipse website

- Sigasi Studio as Plugin in your own Eclipse installation:

- Eclipse 4.7.3a Oxygen up to Eclipse IDE 2019-03

- Java JRE 8

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 300MB of free disk space.

Sigasi Studio 4.5.1 point release

On September 30 we released Sigasi Studio 4.5.1. This release fixes the following reported issues:

- The EGit plugin can’t be updated in Sigasi Studio 4.5.0 stand-alone

- Avoid a pop-up error dialog when a graphical view is opened for the first time on Linux

- VHDL formatting: formatter does not remove whitespace before

`attributes - VUnit integration: VUnit empty script error is not removed when the script is fixed

Sigasi Studio 4.5.2 point release

On October 17 we released Sigasi Studio 4.5.2. This release fixes the following reported issues:

- The Quick Fix to declare all signals in a port map sometimes is very slow

- The Quick Fix to declare all signals in a port map can hang the user interface

- The Open Declaration context menu item does not work in VHDL

- The Occurrence highlighting occasionally does not work

- Navigating using Ctrl+Click can be very slow

Thanks for all the bug reports and enabling Talkback.