The Sigasi Studio 4.11 release continues to improve your Verilog, VHDL and SystemVerilog coding experience. This release brings many improvements. We introduce VHDL 2019 support, improved block diagrams and much more. Read on for more details.

We are also trying something new: a quick feedback question for our next release:

Cast your vote.

VHDL 2019

This release introduces VHDL 2019 into Sigasi Studio. To make use of the improved language features and APIs you need

to set your VHDL project (or a single file) to VHDL 2019 and update the std and ieee libraries:

- Update the project version: Right-click the project (or file) and select .

- Update the

stdandieeelibraries: Right-click theCommon Librariesfolder, and select

We have made a screencast to demonstrate this.

The following VHDL 2019 features are now supported:

- All the new VHDL 2019 APIs in the updated

stdandieeelibraries - Functions now know the type of the receiver of the return valueVHDL

function convert_to_slv(constant i: in integer) return TResult of std_logic_vector is variable result: TResult; begin -- Can now access attributes of the receiver of this return value result := std_logic_vector(to_signed(i, result'length)); return result; end function; -- Now we can do the following x <= convert_to_slv(i); -- Instead of x <= std_logic_vector(to_signed(i, x'length)); - The ending

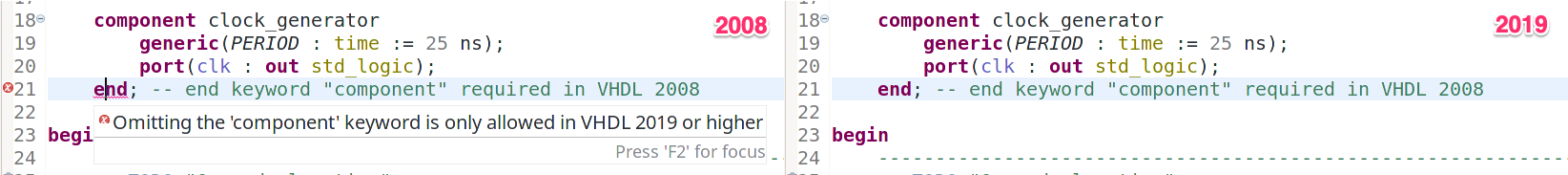

componentkeyword in a component declarations is now optional

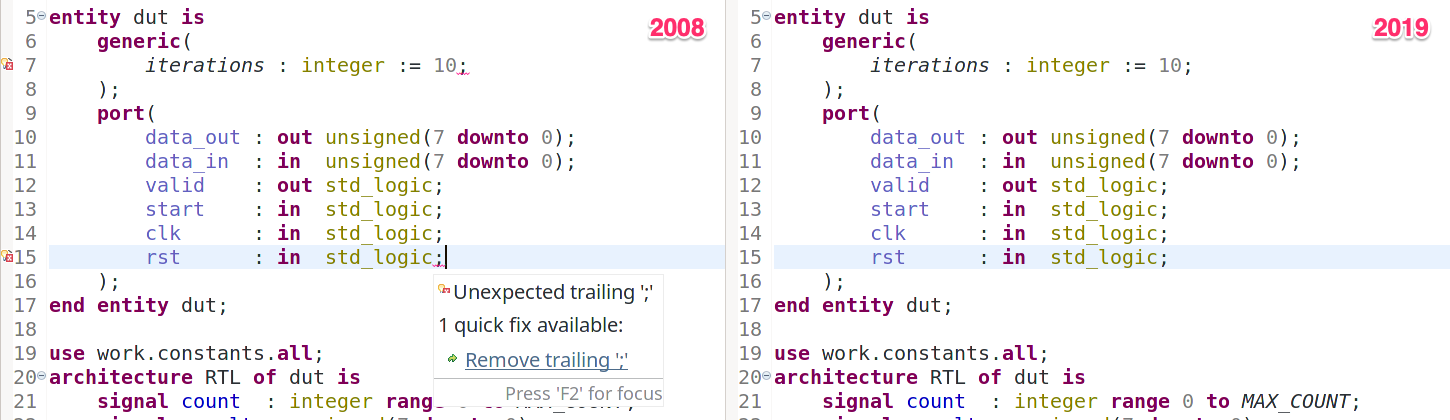

- A trailing semicolon in

port,genericandparameterlists is now allowed

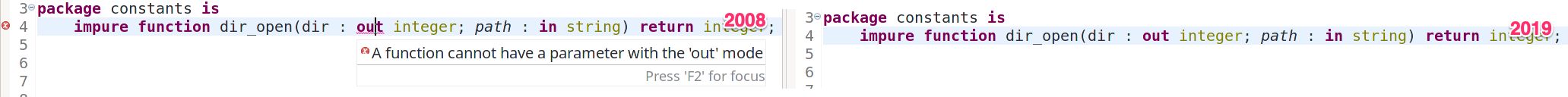

- Parameters of

impure functions can now haveinoutandoutmodes

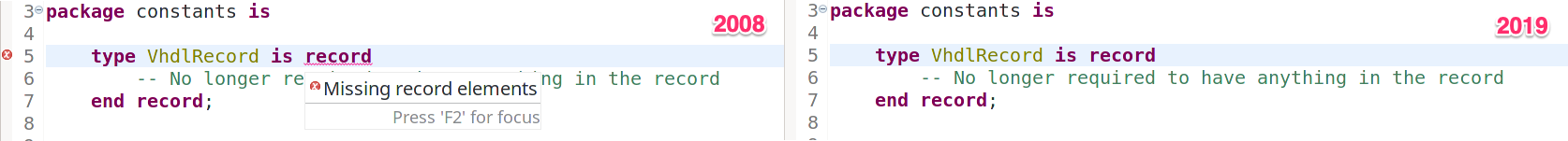

recorddeclarations can now be empty

- Qualified expressions’ operand is now optionalVHDL

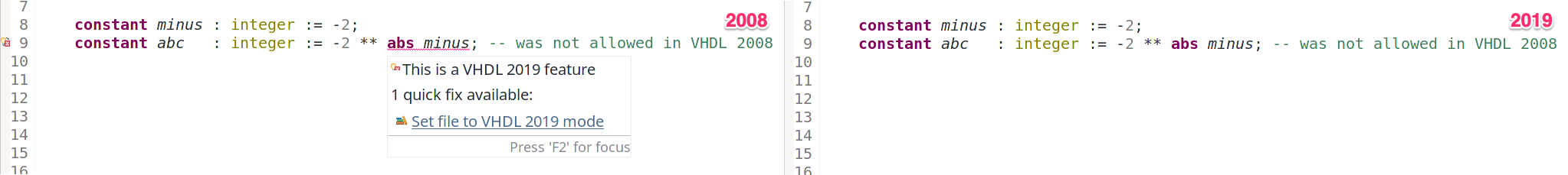

-- Value of "abc" is an empty value of the type std_logic constant abc : std_logic := std_logic'(); - Improved syntax of power expressions (

**)

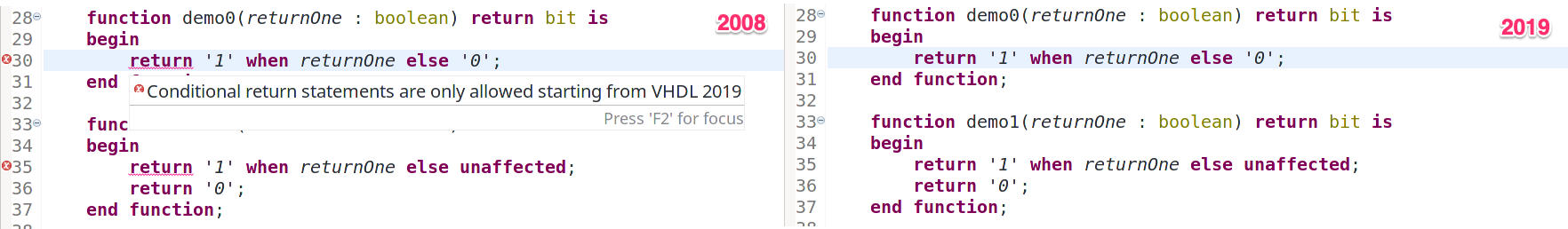

when-elseandunaffectedexpressions are now allowed inreturnstatements

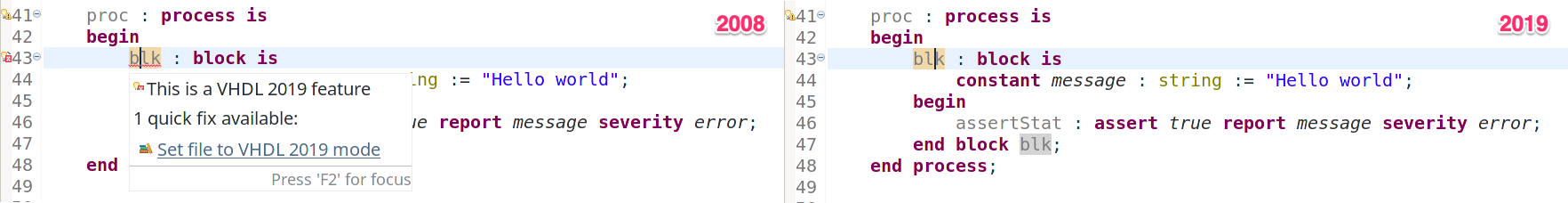

- Sequential

blockstatements

Other VHDL improvements

- Default values for

generics are now part of the autocompleted component declaration

- Quick fix multiple capitalization issues at once in the problems view

- Improved auto indentation for

procedures - Improved alignment during formatting of

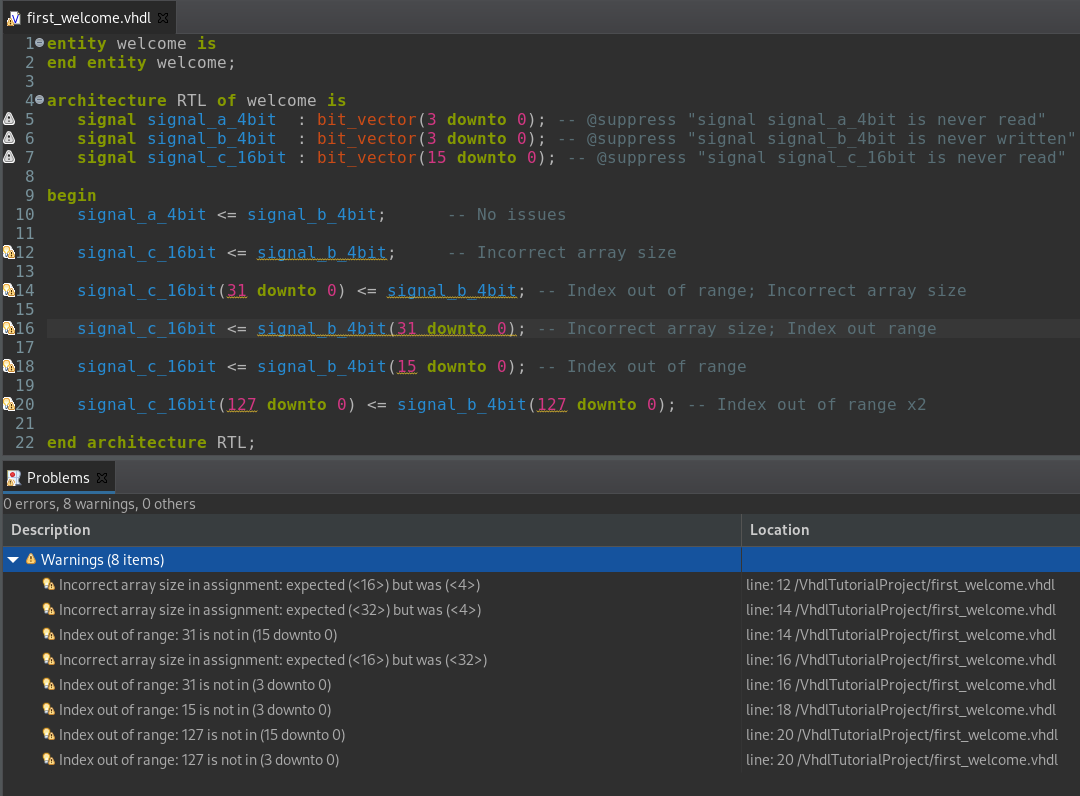

procedurearguments - Added a new linting check to detect index out of range and incorrect size for arrays

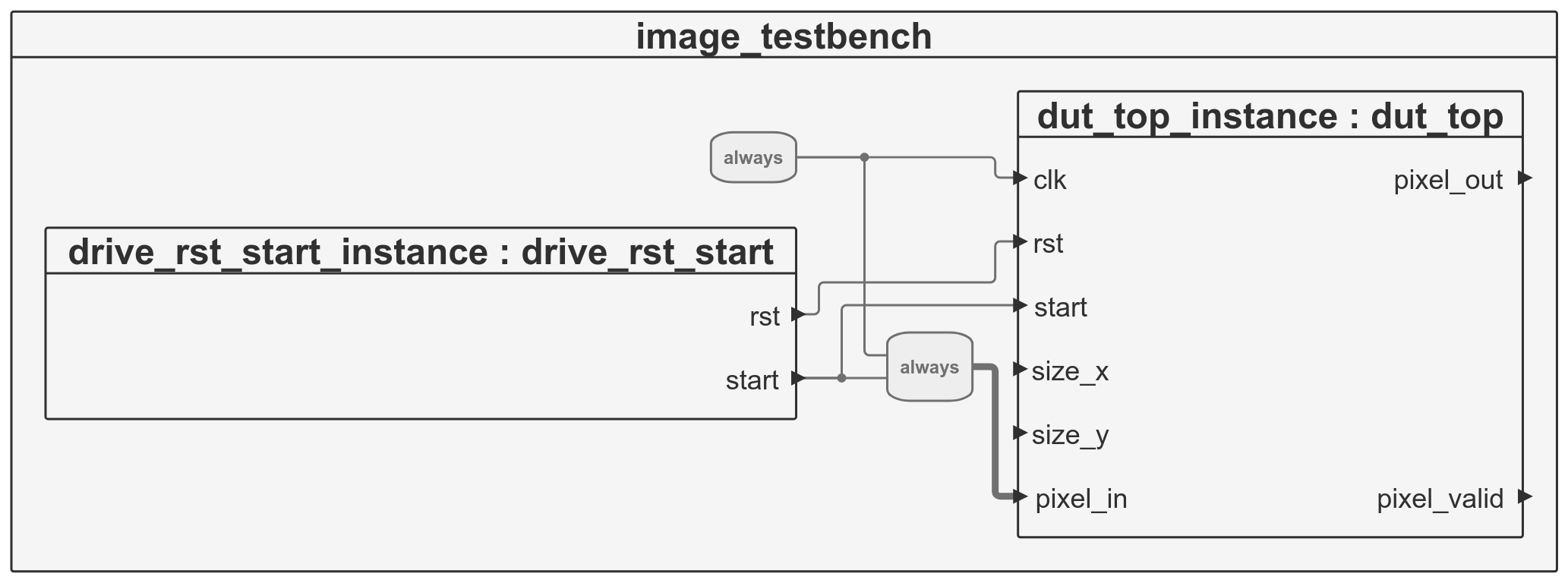

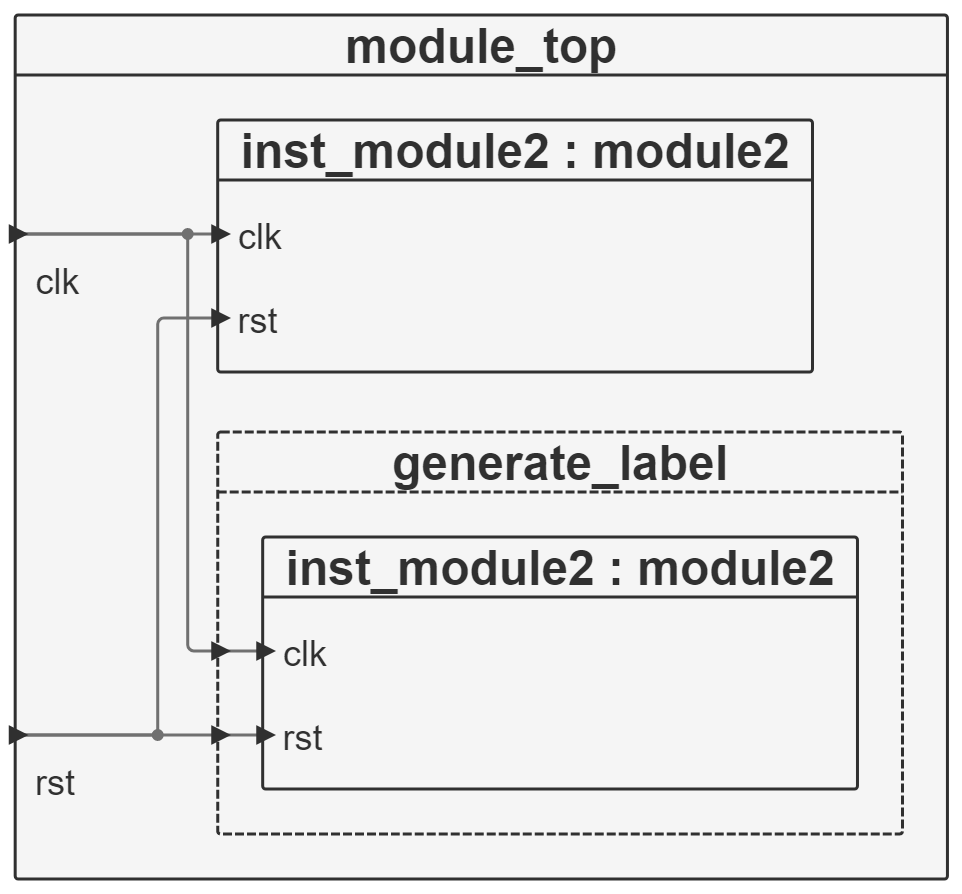

Block Diagram improvements

Sigasi Studio 4.11 also brings many improvements to the Block Diagram view.

We improved the Verilog and SystemVerilog code analysis which refined the displayed connections. We also improved the way we draw connections which results in speed improvements.

In addition we also added support for:

- Verilog

generate blocks

- VHDL

blockstatements

- Mixed language direct instantiations: Verilog modules are now displayed in VHDL architectures and VHDL entities in Verilog modules.

Verilog and SystemVerilog improvements

- Reduced memory consumption and improved code analysis speed, especially when you are using parameterized classes

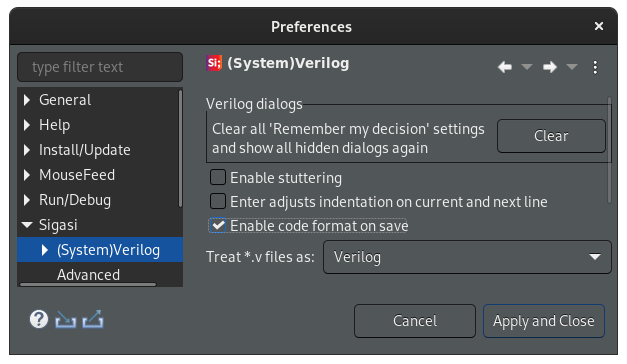

- Added the option to format on save

- When SystemVerilog

.sv-files are used as include files, they are now automatically only analyzed as include file and not as as regular SystemVerilog source file. This results in fewer unexpected syntax error messages. - Anonymous UDP instances are now shown in the outline

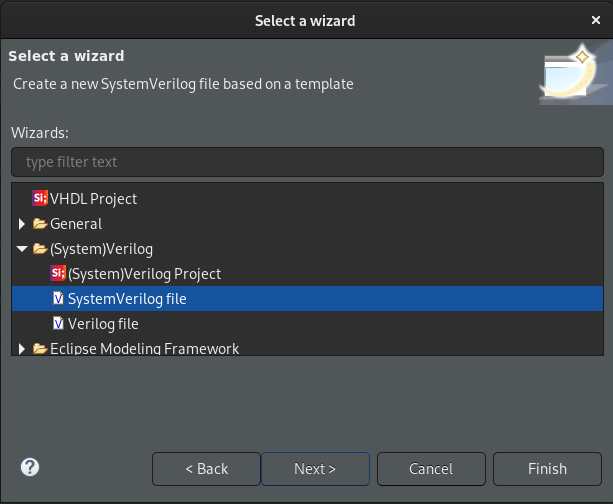

- Added

New SystemVerilog Filewizard

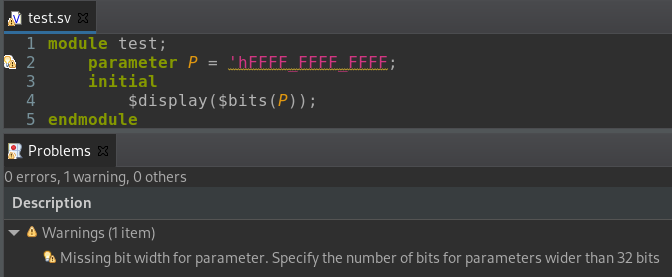

- Added a new linting check to detect > 32-bit parameter initialization without width specification (STARC Verilog, rule 1.1.4.9)

- Added a new linting check to detect improper use of 4-state net date types

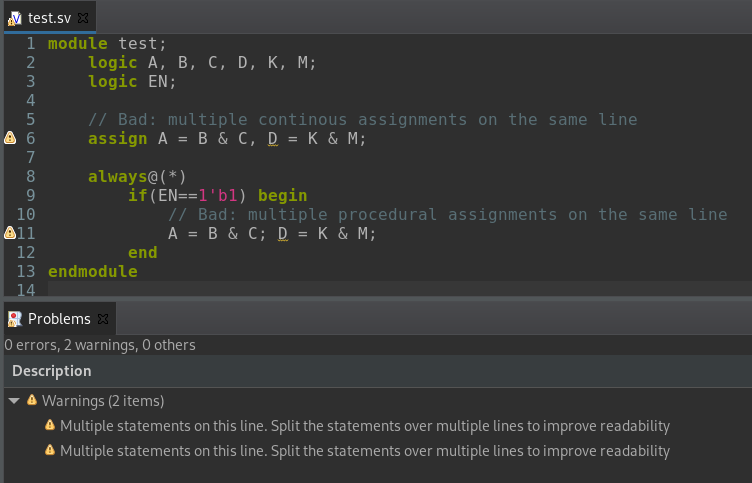

- Added a new linting check to report when there are multiple statements on the same line

- Support conditional operator (ternary operator) in transitions of state

- Improved checking of duplicate, unresolved, too many or missing formals in instantiations

Other New and Noteworthy Changes

- Improved monitoring and canceling of external compilers

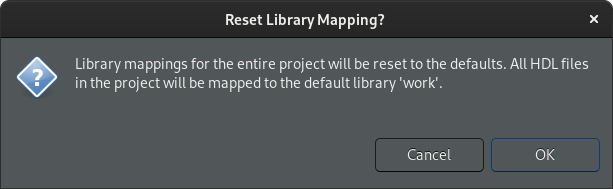

- We now show a warning dialog when you select to make sure users do not accidentally reset their library mappings (Note that this is recoverable by opening the

.library_mapping.xmlfile and reverting it to an earlier version)

- The Report Encrypted Regions check no longer underlines whole regions with red squiggly lines. It now shows just one marker instead

- Improved error reporting for documentation export when the exported resources already exist and can’t be overwritten

- Improved punctuation in our messages

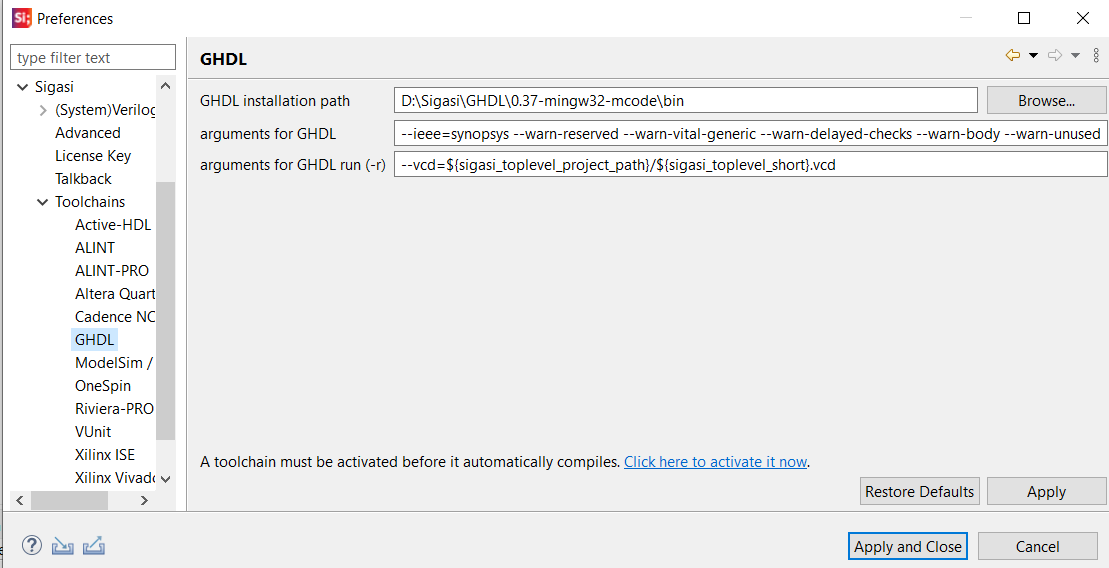

- Split of simulation arguments to a separate field in the toolchain preferences for GHDL

- We updated Eclipse in the standalone Sigasi Studio to Eclipse 2020-12

- Improved hovers in Graphics Configuration files hovers

- Updated the Xtext dependency to 2.24.0

- Chromium was Updated to 76.0.12

- Sigasi Studio is now bundled with a Java 15 runtime environment. We also improved the way we bundle the JRE in Sigasi Studio. It is now bundled as an updatable feature. So from now on, the JRE is automatically updated with Sigasi Studio.

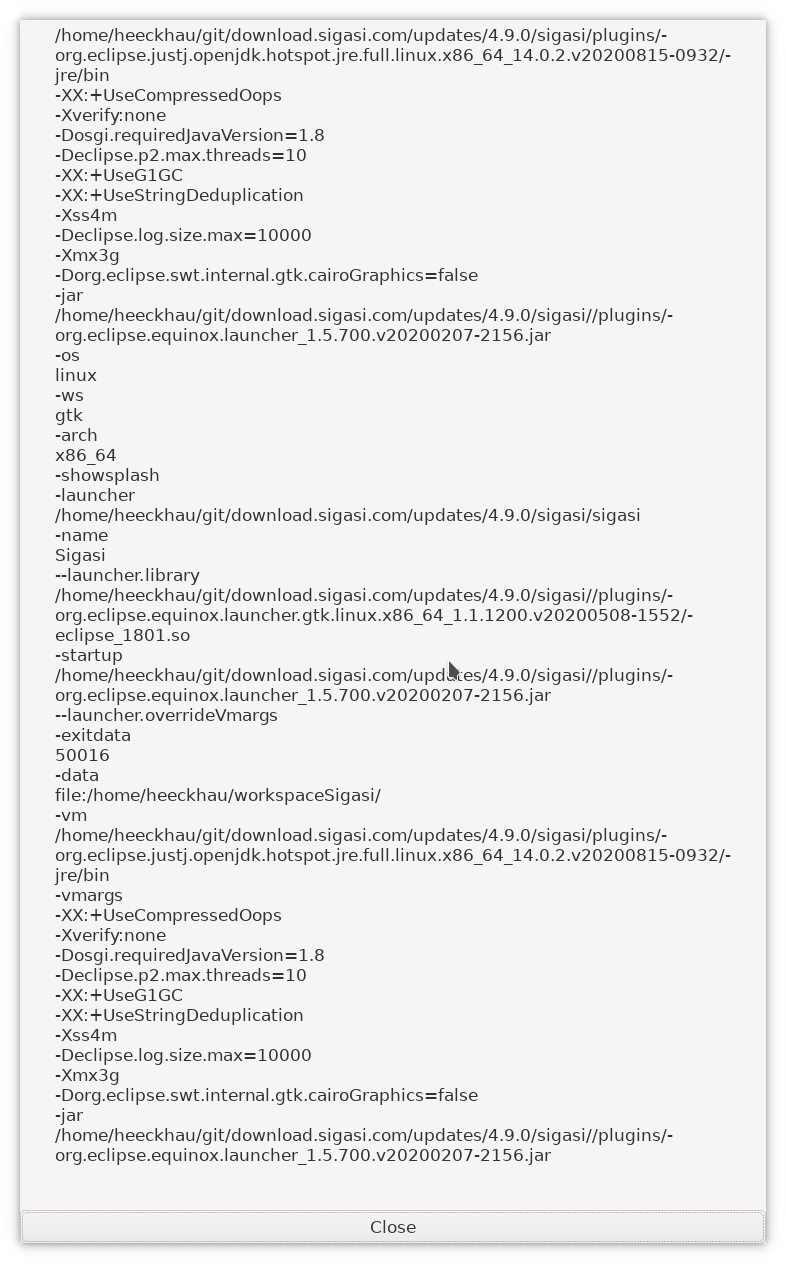

Note that you may run into the error dialog below, when you restart Sigasi Studio after the update because the JRE has changed. If you close the dialog, and restart Sigasi Studio manually, everything should work as expected

ALINT Deprecation warning

We plan to remove the legacy ALINT implementation in Sigasi Studio in the next release (4.12). We assume everybody has updated to the newer ALINT-PRO by now.

Bug fixes

- Fixed random hover errors in unsaved editors

- Fixed disappearing edges on hover in nested states in statemachines

- Aligned case-sensitivity of Graphics Configuration files to VHDL and Verilog

- Removed context menu from the documentation view

- Fixed unexpected sound effect when opening the documentation view

- Fixed running of all VUnit tests in a project

- Fixed broken editor when file for the editor was removed while Sigasi Studio was not running

- Renaming a graphics configuration file while it’s open in an editor now works as intended

- Fixed an error when quickly pressing the buttons in Block Diagram view toolbar

- Fixed graphics not using all available space when scaling is enabled in the OS

- Made suppressing of tutorial project creation work again

- Allow Sigasi Studio to be used as external editor in Vivado on Linux again

- Fixed the Set Top button in the Hierarchy View when editing external files

- Fixed a rare case in which the cursor jumped to the start of the file after formatting

- [VHDL] Fixed structured selection no longer selecting single words

- [VHDL] Fixed corruption of VHDL outline, block diagram and hovers in unmapped files

- [VHDL] Fixed a rare issue when formatting aggregates with named associations

- [VHDL] Fixed hover for bitstring literals

- [VHDL] Added an autocomplete template for

procedureprototypes - [VHDL] Now allow (micro)seconds without a space between the numeral and the unit for time literals

- [VHDL] Fixed scoping/linking issue with declarations in block statements

- [VHDL] Improved the internal VHDL interpreter (hovers, linting)

- [Verilog] We no longer show errors in the problems view for files that are excluded from build and are not included anywhere

- [Verilog] Fixed linking support for

randsequencein broken code - [Verilog] Fixed outline rendering for nested types

- [Verilog] Fixed false positive in 4-state net type validation

- [Verilog] Fixed false positive warning for default type arguments when class was declared as forward typedef before

- [Verilog] Fixed false positive error for property operators

- [Verilog] Fixed false positive error for multiclock SVA properties

- [Verilog] Fixed false positive error for SVA property operators with

alwaysas an operand - [Verilog] Fixed false positive error for

first_matchin sequences - [Verilog] Fixed missing autocomplete for

`includefiles - [Verilog] Fixed preprocessing when an

`includedirective is directly followed by more tokens - [Verilog] Fixed false positive errors and warnings in include files that are excluded from build but are included in files that are in the build

- A lot of other issues we could fix thanks to your Talkback reports

System requirements

- Sigasi Studio Standalone is supported on:

- Windows: Windows 10 (64 bit) or newer

- macOS 10.15 Catilina or newer

- Linux: Red Hat Enterprise Linux RHEL 7.7 (64 bit) or newer

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver

- Sigasi Studio depends on

- More information on supported OSes can be found on the Eclipse website

- Sigasi Studio as Plugin in your own Eclipse installation:

- Eclipse 4.8 Photon up to Eclipse IDE 2021-03

- Java JRE 11

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 300MB of free disk space.

Sigasi Studio 4.11.1 point release

On March 30, we released Sigasi Studio 4.11.1. This release fixes the following reported issues:

- Allow correct updates/installation of Sigasi Studio Eclipse Plugin in recent Eclipse installations (in particular Eclipse 2021-03 )

- [VHDL] Fixed formatting for specific types of port map and aggregate combinations

- [VHDL] Allow formatting of files that contain encrypted regions

- [VHDL] Enabled the VHDL 2019 Quick Fix for all VHDL 2019 related errors

- [Verilog] Improved highlighting of

localparams in dark themes - [Verilog] Fixed a rare issue where hovers were not being shown

Thanks for all the bug reports and enabling Talkback.