We are proud to present the Sigasi Studio 4.15 release. This release adds formatting of Verilog and SystemVerilog using the Verible formatter, and support for VHDL 2019 is being extended with support for instantiated protected types. As always, there are many other improvements that enhance speed and usability to give you a better experience.

Verilog Formatting

Sigasi now ships with Verible built-in. Verible is an ambitious (System)Verilog formatter that is agnostic to macro invocations and includes and therefore produces a consistent formatting result also in heavily preprocessed code.

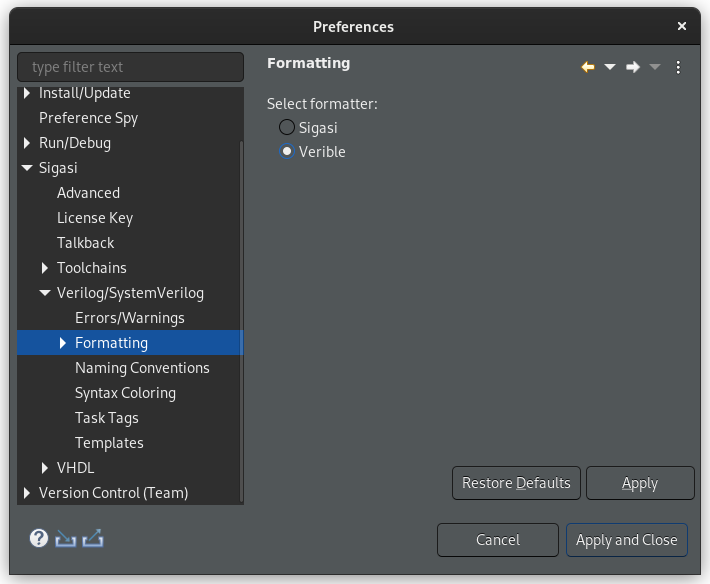

You can enable the Verible formatter for your installation by going to Window > Preferences > Sigasi > Verilog/SystemVerilog > Formatting.

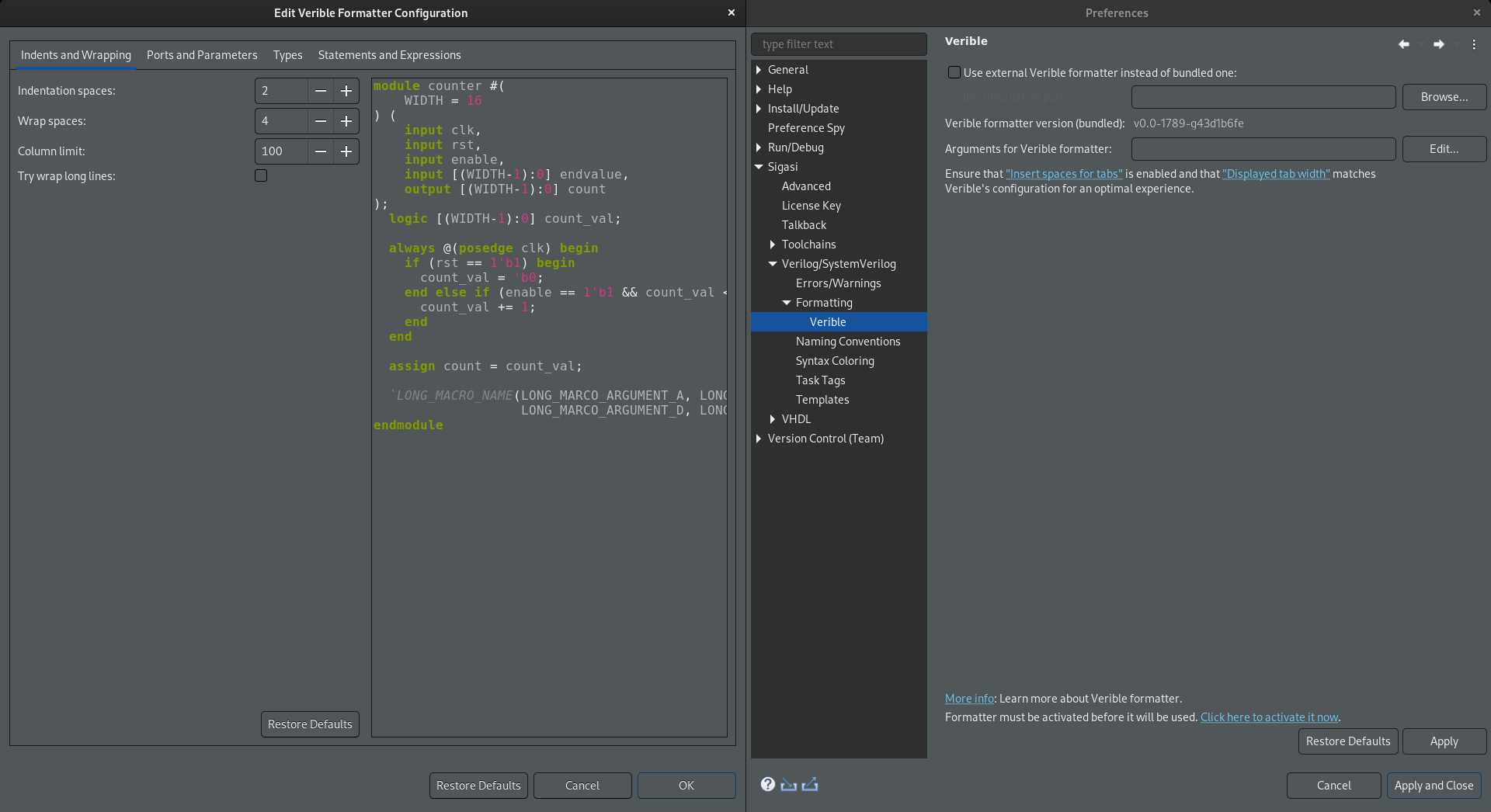

Sigasi ships with a recent version by default, but if you’d rather run your own Verible installation, this can be achieved in Window > Preferences > Sigasi > Verilog/SystemVerilog > Formatting > Verible. This page allows you to customize its rules by pressing the Edit... button.

To see this in action, you can have a look at our screencast.

VHDL 2019

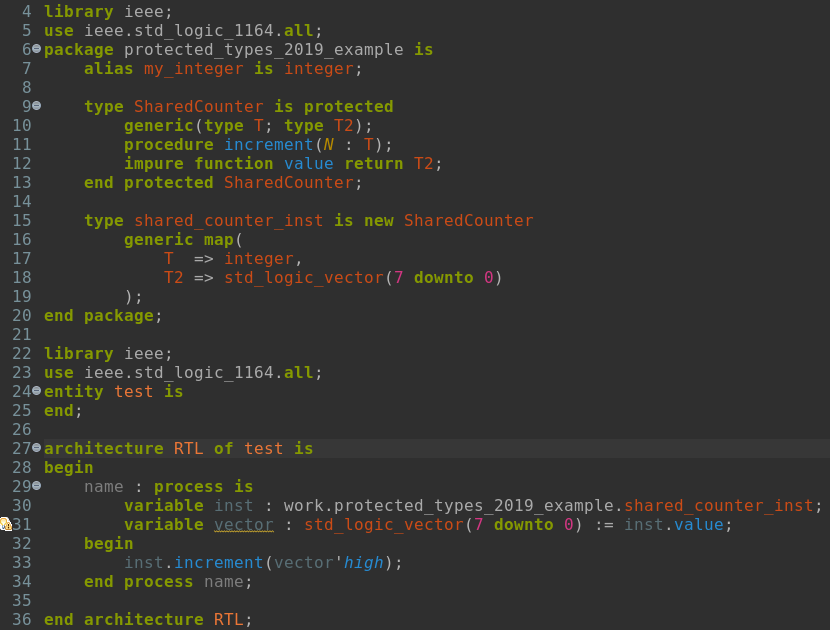

In this release we’ve added support for VHDL 2019 instantiated protected types. Defining one of these creates a generic-mapped protected type, equivalent to one created through a protected type declaration and its respective protected type body.

Protected type instantiation shared_counter_inst of SharedCounter

New and Noteworthy Changes

- Greatly enhanced File Search (Ctrl+H) speed

- The Quick Outline initial expansion has been adjusted such that modules, entities, and classes are immediately expanded. This gives a better overview of the design at a first glance.

- Improved the consistency of the ordering, grouping, casing, and punctuation in the preferences and

New...dialogs - The performance of instantiation autocompletes has been greatly improved

- The performance of autocompletes in general has - independently from the previous item - also been greatly improved

- Autocompleting design unit (

entity,component, or Verilogmodule) instantiations is now supported for design units denoted by an extended identifier (e.g.\Cool Name$\in VHDL, or\$amazing^namein Verilog) - Added the ability to run performance logging to help us analyze potential user issues

- The colors used in the

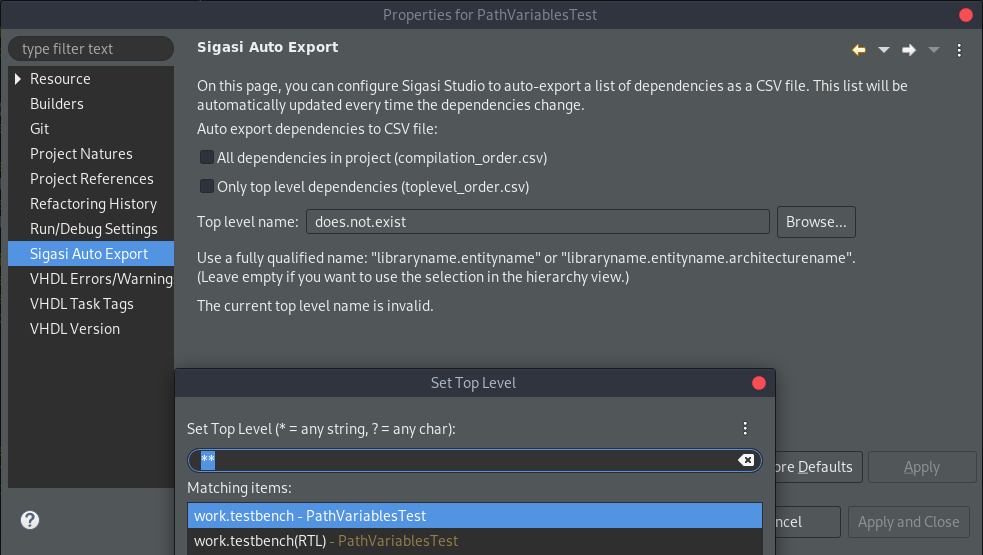

Set top leveldialog have been made consistent with Sigasi’s other views - The Sigasi Auto Export now validates that the given

Top level nameexists, and gives you an option to browse through valid ones - Improved responsiveness when enabling or disabling Talkback

- The

Verilog VersionandVerilog Errors/Warningspages are now hidden in the VHDL file properties. The same was done for the corresponding VHDL pages in Verilog file properties - The selected project or top level is now always visible in the export documentation dialog

- The link to Sigasi’s website in the exported markers document now uses HTTPS instead of HTTP

- The Hierarchy, VUnit, Net Search and Libraries View now honor the single-click navigation preference (

Preferences > General > Open mode) - Added the option to disable smart caret positioning in identifiers, both in VHDL and (System)Verilog. Smart caret allows you to easily jump between words in identifiers, no matter if you use camelCase or snake_case, by using Ctrl+Left arrow and Ctrl+Right arrow.

- [VHDL] Added a red squiggly line under subprograms in packages when the corresponding subprogram body in the package body is missing

- [VHDL] Added new constructs to the outline:

- labels for concurrent statements

- package and type declarations in entity generic lists

- [VHDL] As setting an

entityas top level does not make sense, trying to set anentityas top level will now always set - or give you the option to select - its architecture as top level - [VHDL] Improved handling of strings at invalid places

- [VHDL] Formatting support has been added for attribute expressions e.g.

integer'image(s_MyInteger + 1) - [VHDL] Autocompleting a function call no longer adds the semicolon at the end. The semicolon at the end is rarely useful.

- [VHDL] Added formatting for generic package and function declarations

- [VHDL] Improved auto indentation of many constructs (type declarations, functions, packages,…)

- [VHDL] The index out of range validation now supports the

openexpression insubtypedeclarations - [VHDL] The VHDL version mismatch Quick Fix can now update your project version

- [VHDL] The incomplete associations Quick Fix now adds the missing associations and also sorts them as in the declaration

- [Verilog] Added variable declarations to the outline, using a qualified path to describe their type

- [Verilog] Added predefined Verilog macros (matching

`SV_COV_*) for use with the$coverage_controlsystem function - [Verilog] Added folding for subprograms

- [Verilog] Changing the default nettype in an included file is now supported

- [Verilog] The selection color in the Preprocessor View now adapts to the theme being used

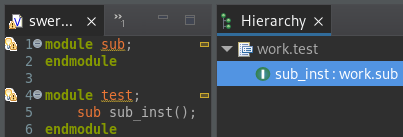

- [Verilog] Verilog

moduleinstantiations are now shown with more detail in the hierarchy view - [Verilog] Non-active preprocessor code is now deemphasized instead of emphasized in the dark theme

- [Verilog] Block diagrams now show more connections, especially towards

alwaysblocks - [Verilog] Improved preprocessor recovery for unbalanced parentheses in preprocessor directives

- [Graphics] Exported graphics now default to

.pngwhen no extension was explicitly mentioned - [VUnit] Added support for custom preprocessors

Updates

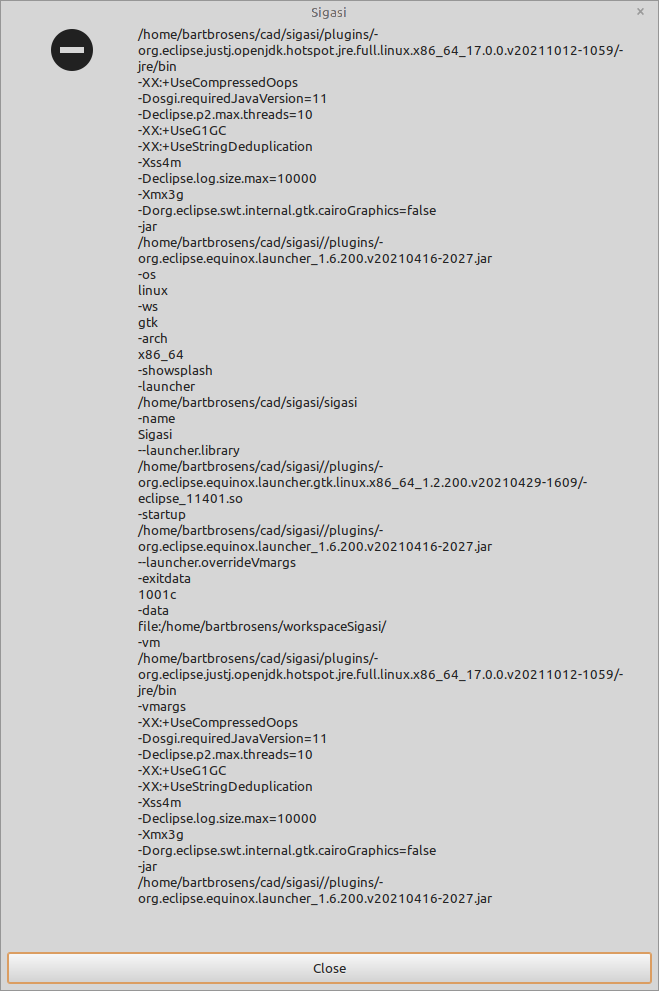

- JustJ (the JRE shipped with Sigasi Studio) has been updated to 17.0.2

Note that you may run into the error dialog below, when you restart Sigasi Studio after the update because the JRE has changed. If you close the dialog, and restart Sigasi Studio manually, everything should work as expected. - The minimum VUnit version required by Sigasi is now

4.5.0 - Sigasi now uses Chromium 80 for rendering graphics and the Documentation View. This improves the performance and stability of these views

- Eclipse has been updated to 2021-12

- MouseFeed - an optional plugin shipped with Sigasi - has been replaced by the Eclipse option

General > Keys > Through mouse click

Bug fixes

- Made unintentionally transparent icons on Windows non-transparent again

- Fixed missing editor support when a file from a closed project is externally opened and the project is opened again

- Fixed rare behavior that caused the outline and the coloring to be applied only after the first edit in a file

- Fixed rare case where editing operations cleared the Find References view unexpectedly

- Fixed selection linking between the libraries view and the editor

- The hover window now sizes more accurately according to its content

- Prevent excessive vmap calls to external compiler when using the same pre-compiled library in multiple open projects

- When instantiating a Verilog module in VHDL, undefined VHDL signals in the instantiation are now flagged

- Fixed PNGs - exported from the graphical views - being cut off for very large designs on low resolution displays

- Fixed the classpath for snapshot_uploader.bat

- Made sure that projects opened through the command line always open

- Fixed documentation generation for simple entities

- [VHDL] Made sure that the

Add missing associationQuick Fix can always be applied - [VHDL] Fixed formatting failure with unbalanced multiline comments

- [VHDL] Fixed rare cases in which the formatter would not apply any formatting

- [VHDL] Fixed name conflicts between components and entities, and components and libraries

- [VHDL] Fixed Smart Indentation after pressing enter at the end of a type declaration

- [VHDL] Made sure the Quick Fix to update the file to VHDL 2008 - when

openis used as a range - is available

package name is

type array_type is array (integer range <>) of string'base;

subtype T is array_type(open)(1 to 10);

end package name;

- [Verilog] Fixed an issue where the cursor in the editor would jump to somewhere else after moving it, when the preprocessor view was open

- [Verilog] Reduced memory consumption during linking

- [Verilog] Made sure to only propose Quick Fixes for valid paths when the argument of an

`includecan not be found in the current include path - [Verilog] When folding a module instantiation, Sigasi now correctly shows the first line of the instantiation

- [Verilog] Fixed labels when using increment, decrement or streaming operators

- [Verilog] Fixed broken hierarchy view for incomplete loop generate statements

- [Verilog] Fixed highlighting of ports in user-defined primitives

- [Verilog] Fixed linking of

- the end identifier in blocks

- incomplete bind directives

- [Verilog] Fixed the values for the

`__FILE__and`__LINE__macros - [Verilog] Fixed resolution of nested include paths

- [Verilog] Fixed focus of the bottom pane in the Class Hierarchy View

- [Verilog] A performance regression in the preprocessor that slipped into 4.14 has been alleviated

- [VUnit] Added missing text in

Browsebutton in project importer - [VUnit]

/is now always used as path separator to save the VUnit location, making it interchangeable between platforms - [VUnit] Made sure the

Browse...button in theAdd VUnit supportdialog allows you to browse - A lot of other issues we could fix thanks to your Talkback reports

System requirements

- Sigasi Studio standalone is supported on:

- Windows: Windows 10 (64 bit) or newer

- macOS 11.6 Big Sur or newer

- Linux: Red Hat Enterprise Linux RHEL 7.7 (64 bit) or newer

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - More information on supported OSes can be found on the Eclipse website

- Sigasi Studio depends on

- Sigasi Studio as plugin in your own Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2021-12

- Java JRE 11 or 17

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 1GB of free disk space.

Thanks for all the bug reports and enabling Talkback.

Sigasi Studio 4.15.1 point release

On April 12 we released Sigasi Studio 4.15.1. This release fixes the following reported issues:

- Hang when typing at a very specific speed with the autocomplete window open

- [VHDL] Missing autocompletes for attributes

Sigasi Studio 4.15.2 point release

On May 17 we released Sigasi Studio 4.15.2. This release fixes the following reported issues:

- [VHDL] Missing autocomplete options before context declaration

- [VHDL]

Open Matching Declarationcontext menu item and keyboard shortcut not working - [VHDL] 2-process

std_logic_vectorstate machines not being detected byState Machinesview