The second installment of Sigasi® Visual HDL™ (SVH™) 2024 introduces over a dozen new SystemVerilog linting rules, an improved Tools and Libraries setup flow, VHDL 2019 Mode Views, Smart Indentation, and vastly improved autocomplete.

TL;DR

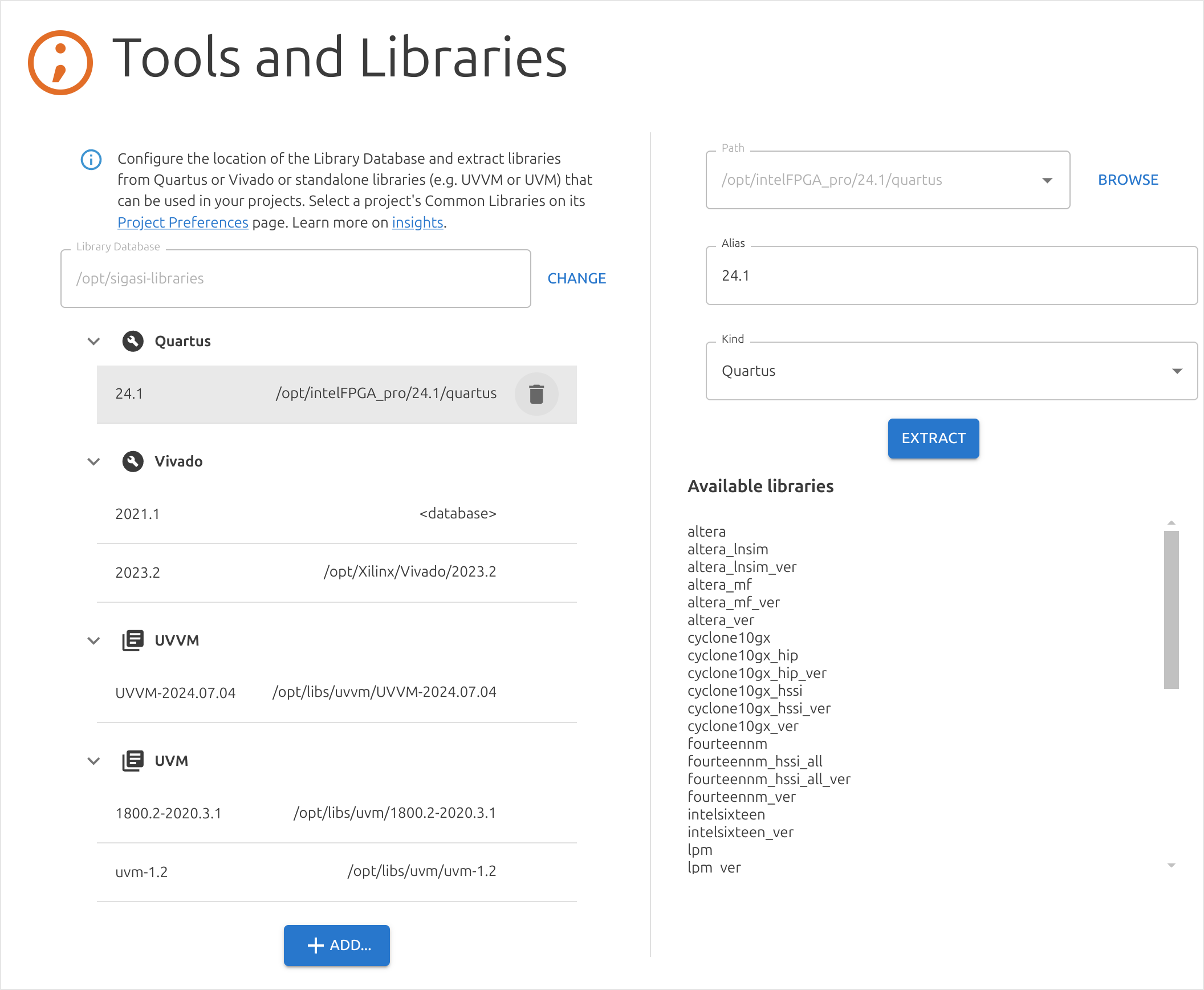

We’ve added over a dozen new SystemVerilog linting rules. They catch version-specific problems, duplicate signals, inheritance loops, and encourage good coding practices.

SVH now includes a simplified user-flow to set up tools and standalone libraries, use them across multiple projects, and share them with the entire team through a Library Database. We now also support the UVVM library natively (similar to the UVM library).

SVH now supports one of the most useful VHDL 2019 features: Mode Views. Mode views allow you to express interfaces, which drastically improves the readability and maintainability of VHDL designs.

Our new Smart Indentation predicts the required indentation level whenever jumping to a new line, never getting in the way.

Continuing the effort made in our previous release, 2024.2 greatly enhances autocomplete performance.

Our CLI introduces a Library extract command to populate the aforementioned Library Database. It has also learned how to deal with SVH projects that use Tools and Libraries.

Last but not least, this release includes a wide range of over 40 bug fixes and improvements.

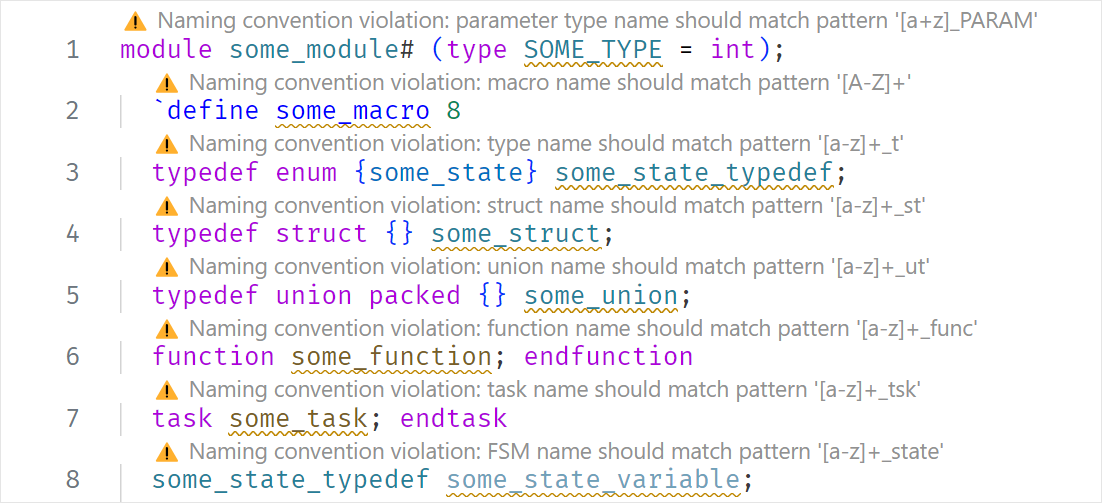

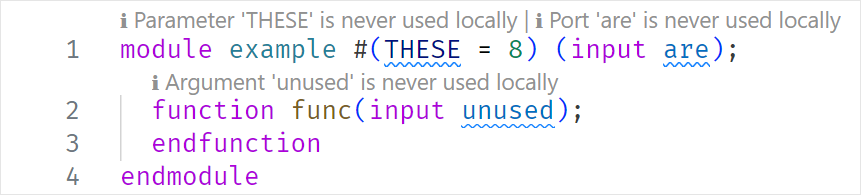

New SystemVerilog Linting Rules and Quick Fixes

SVH linting rules ensure high-quality designs, and with these new additions, your code will be even more reliable and optimized.

New Naming Conventions

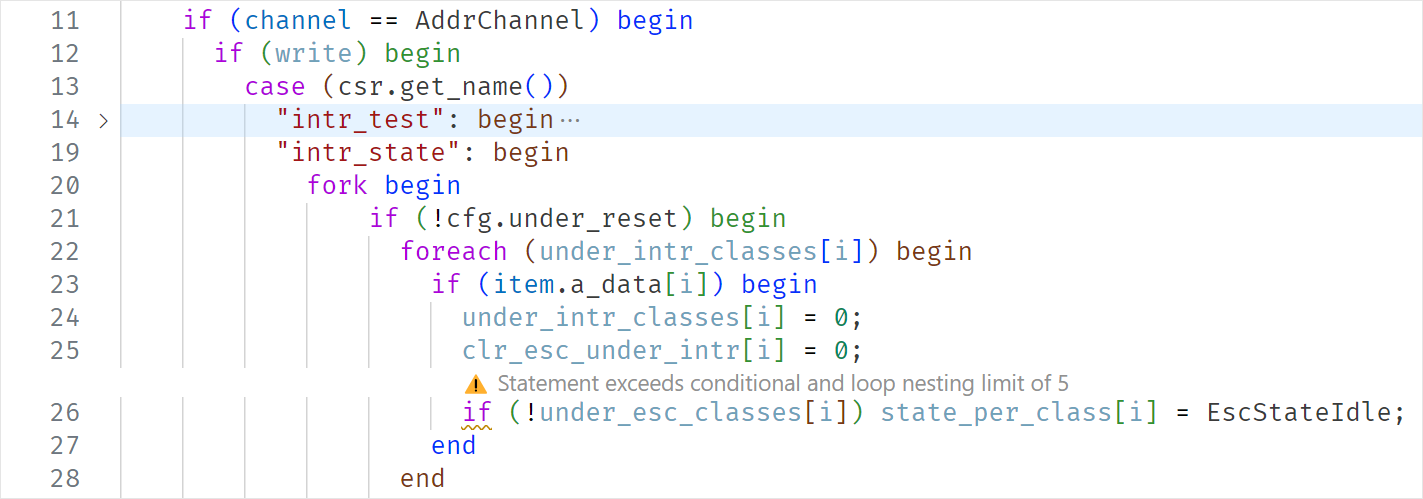

Deep Nesting of Conditional and Loop Statements

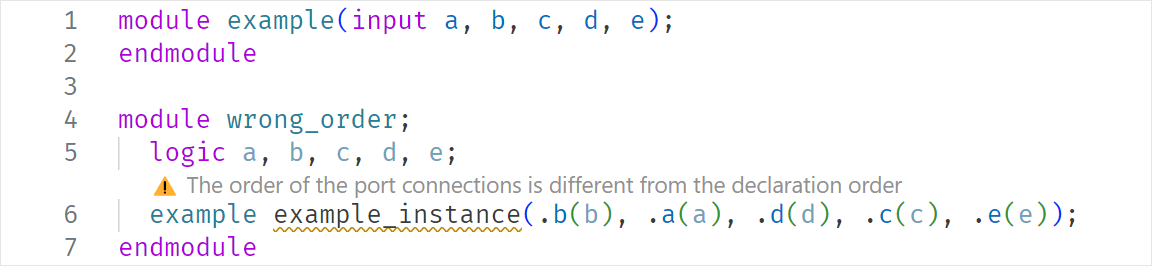

Order of Named Declaration List Does Not Match

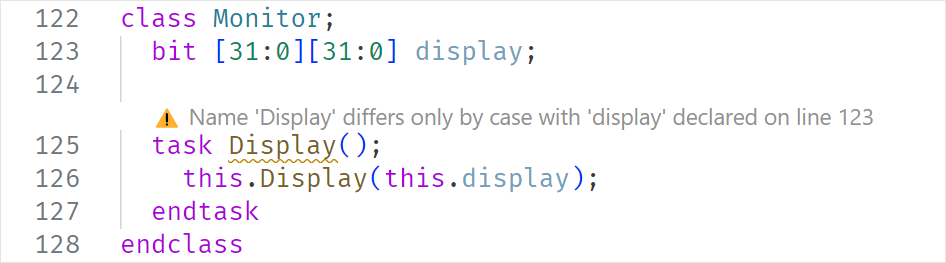

Names Differing Only by Case

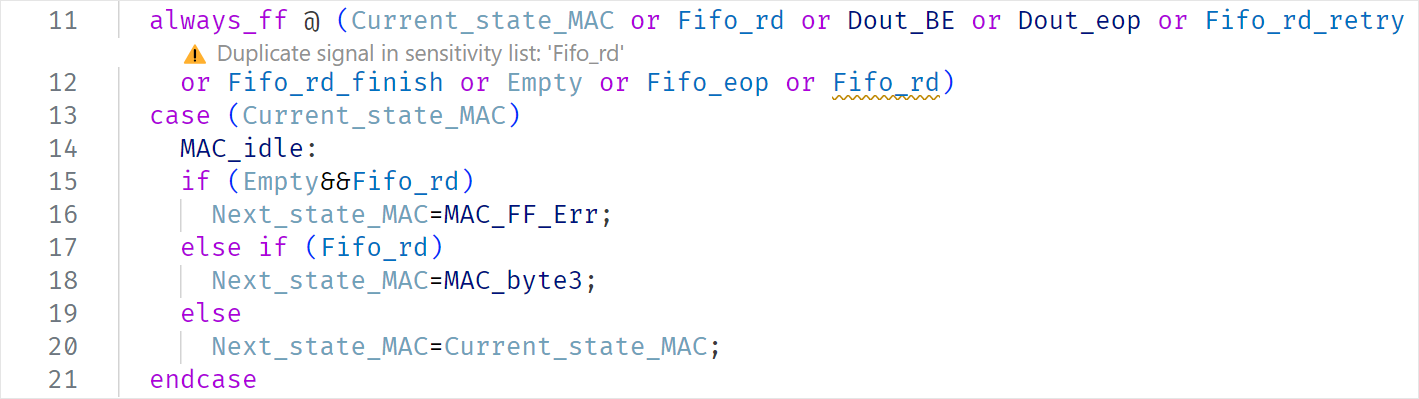

Duplicate Signal in Sensitivity List

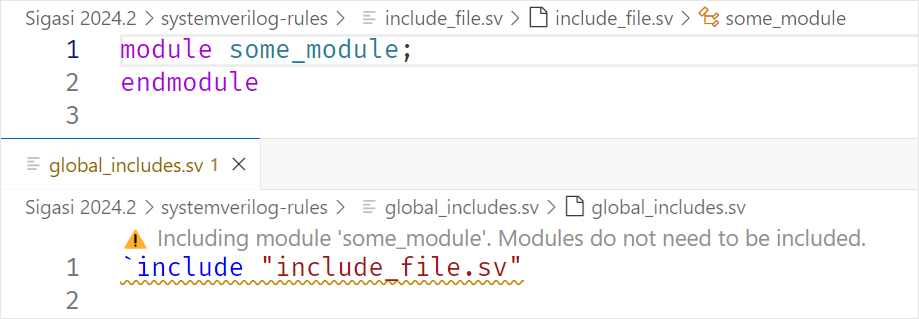

Include of Globally Available Declaration

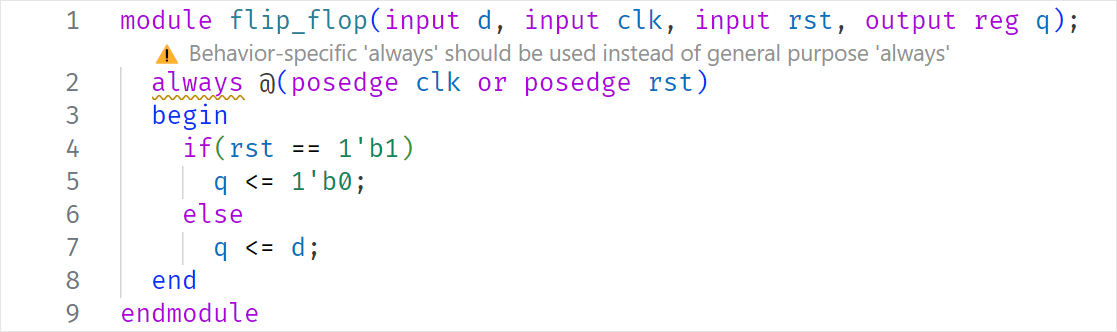

Encourage the Usage of Behavior-Specific Always Constructs

always_[comb|latch|ff] constructs introduced with SystemVerilog should be used in favor of the general purpose always. They describe the intent, provide semantics that improve readability, and can be checked for correctness by tools. A Quick Fix makes it easy to adopt this good practice.Check Locally Unused Ports, Parameters, and Arguments

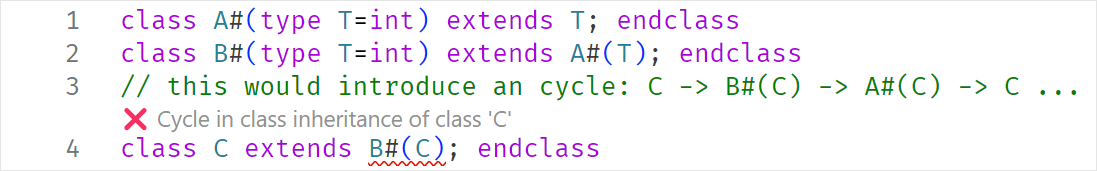

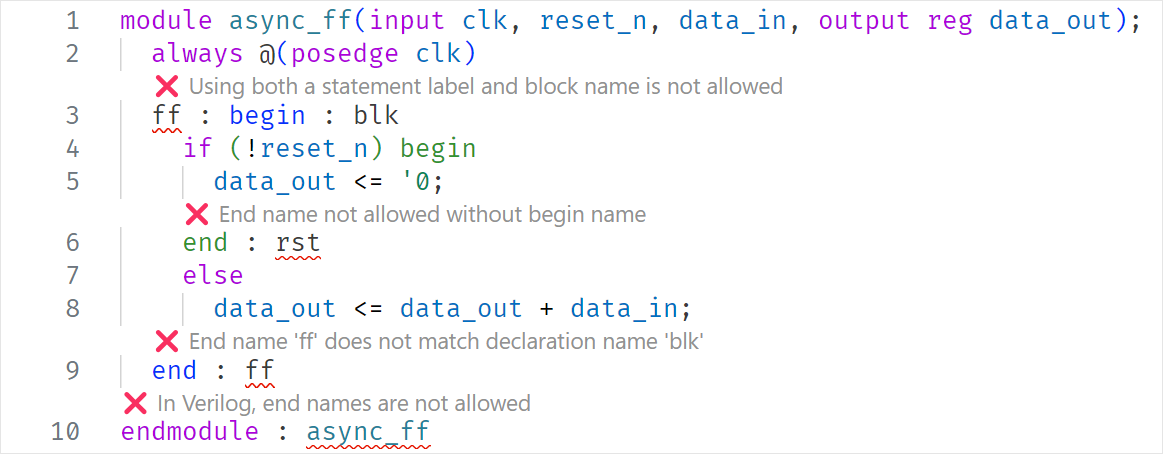

Cyclic Class Inheritance

Various Checks for Labels

Quick Fix to Change Version

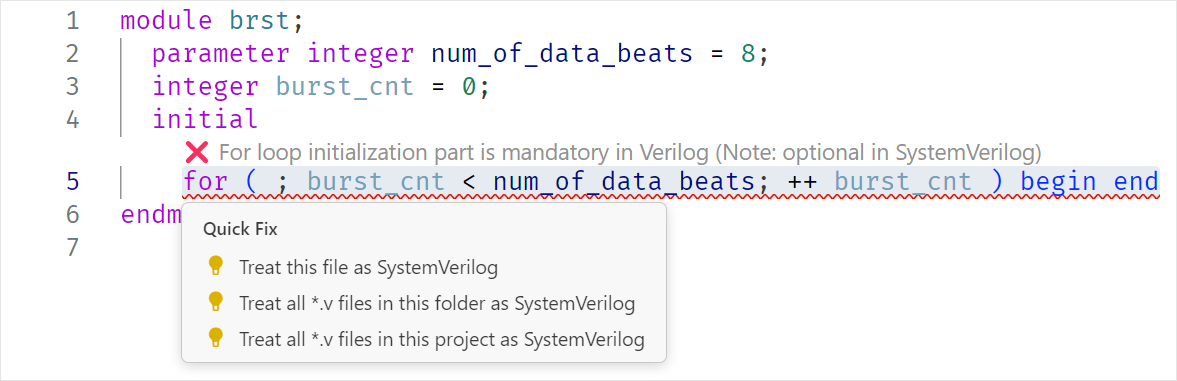

Improved Tools and Libraries Setup Flow

The Tools and Libraries settings page lets you add tools and libraries. SVH supports UVM, UVVM, and custom libraries, as well as libraries that are available with Vivado or Quartus installations.

When added, libraries are extracted to a Library Database. You can then share this database among multiple Sigasi projects and distribute it among your team to ensure everyone uses the same library versions. Learn more

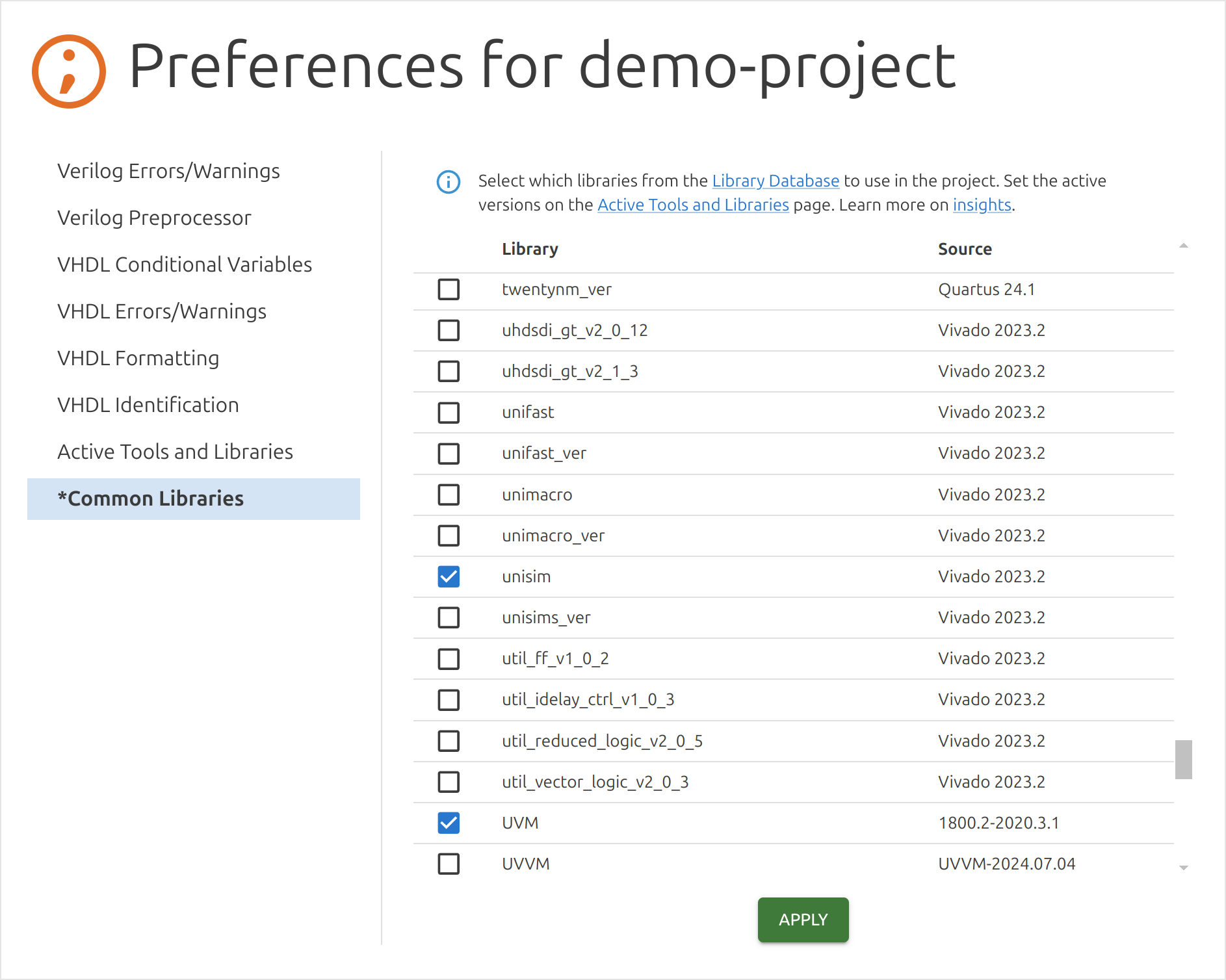

Once all the libraries you need are in the Library Database, you can select the libraries you want to use in your project on the Common Libraries project preferences page (Right-click the project in Sigasi Projects and click Open Preference View).

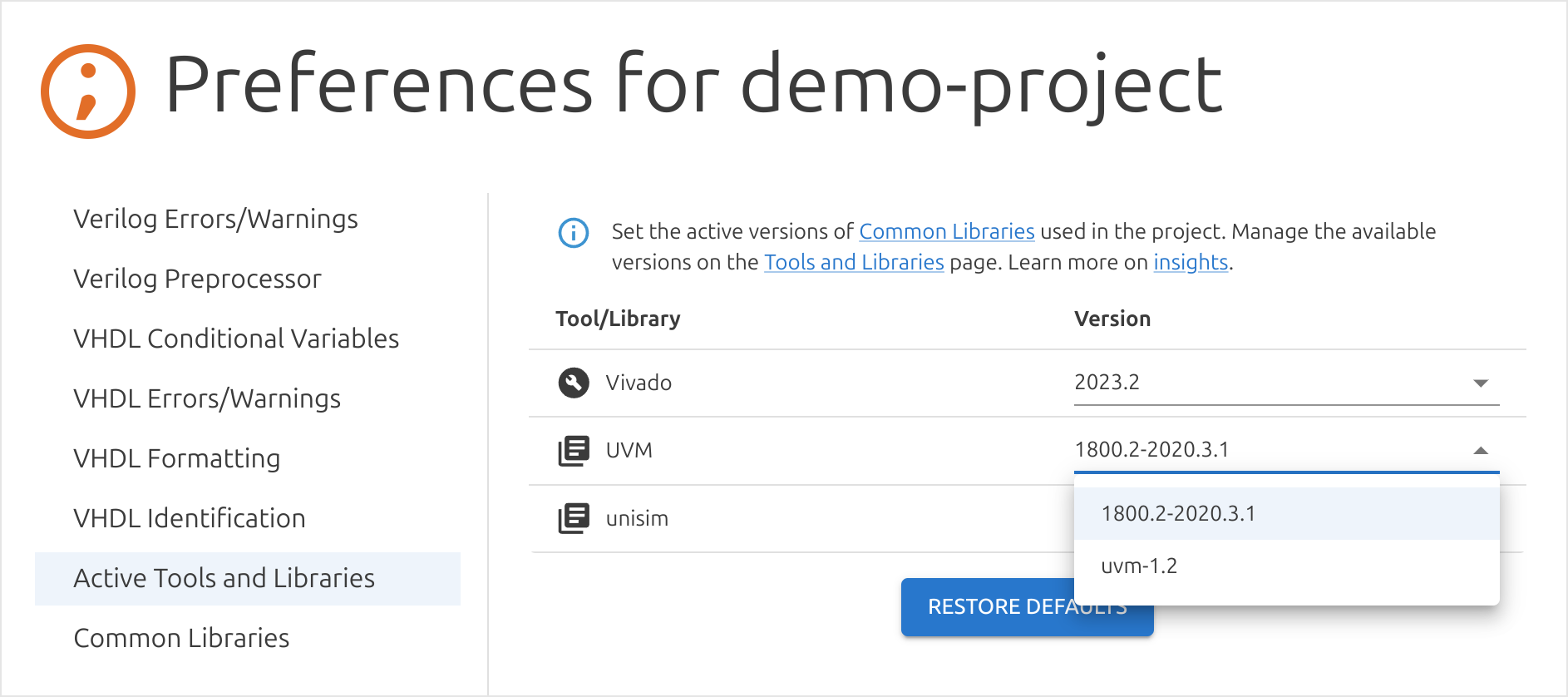

If there are multiple versions of tools or libraries available in the Library Database, you can select the version that a project should use on the Active Tools and Libraries project preference page.

Note this new feature required our internal format to be overhauled.

See our upgrade instructions.

VHDL 2019 Mode Views

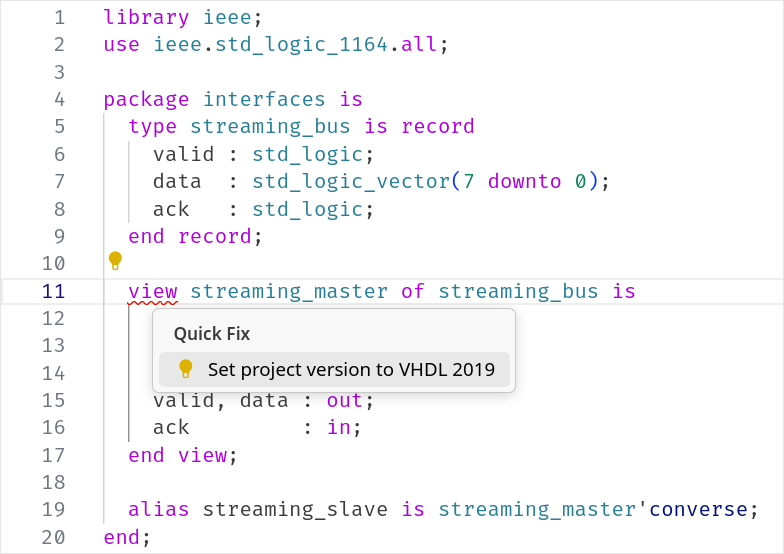

Mode views are SVH’s most requested VHDL 2019 feature. They allow you to define the direction of a collection of ports, making not only the type but also the directions reusable. Their closest comparison is SystemVerilog modports. You can start using mode views by configuring your files to VHDL 2019, which is easily done through a Quick Fix. Learn more

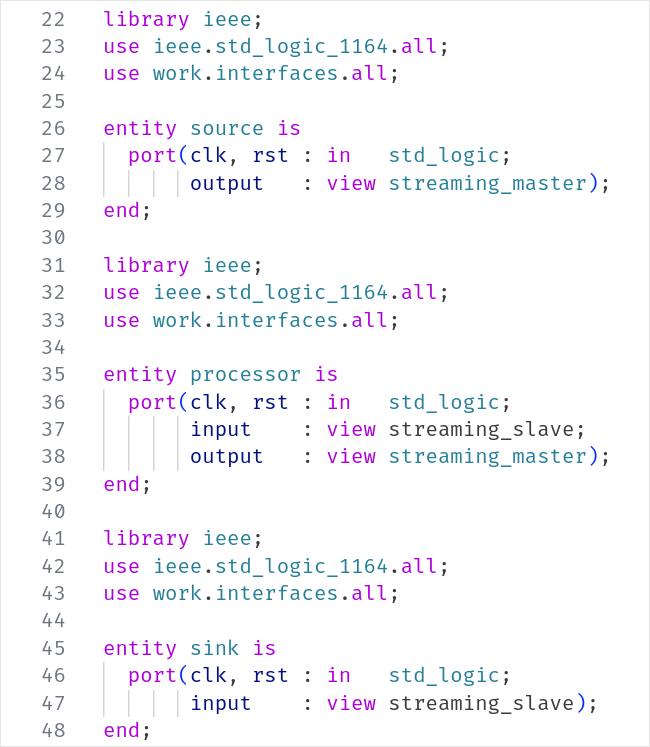

Now that the mode views are understood by SVH, we can put them to good use.

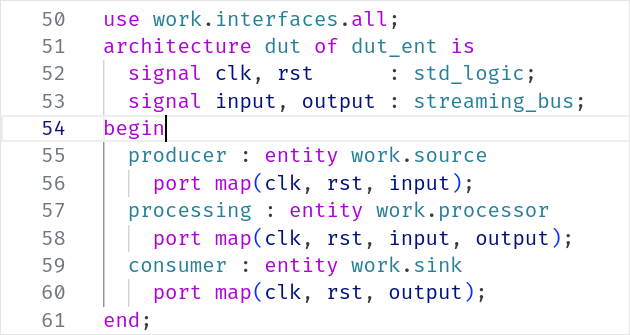

Finally, we declare a dut that internally uses the view modes.

You will be pleased to learn that mode views work throughout SVH, from syntax, linting rules, formatting, and hovers to Net Search and Graphical Views.

We even added two new linting rules, ensuring mode views are correctly defined.

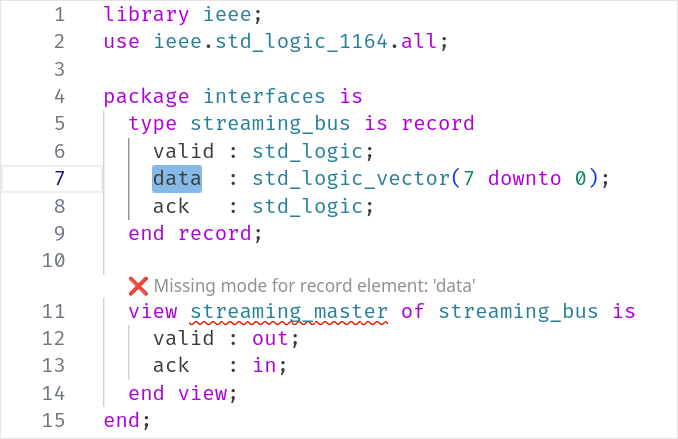

Missing Mode for Record Element in Mode View

The VHDL language specification mandates that every member declared in the record must have their direction defined in the associated mode view.

The missing elements can be added through a Quick Fix.

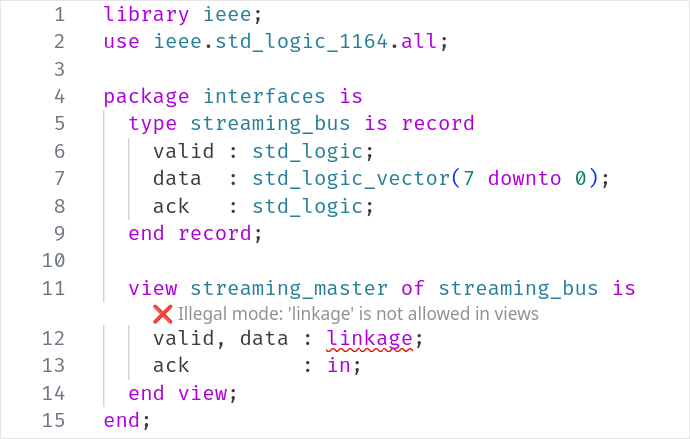

Illegal Mode View Element Mode

linkage as a direction in mode views.Smart Indentation

Whenever you jump to a new line, SVH seamlessly predicts the indentation level required, saving you a few precious keystrokes and eliminating the need to run the formatter constantly. Learn more

Heap Size Visualization

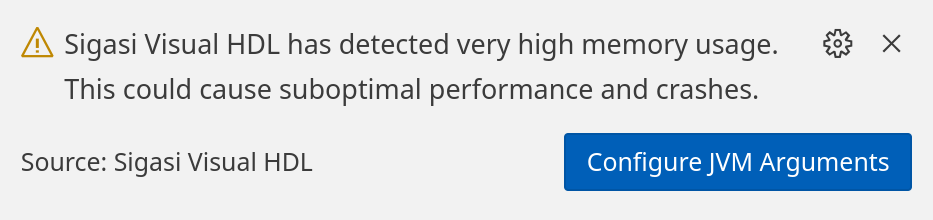

Resource management is always a balancing act. You might have wondered whether SVH uses all the memory you give it or whether it could use some more. Wonder no more! You can see the used and maximum assigned memory for SVH in the Status Bar. With this knowledge, you can tweak SVH to fit your project by optimizing your project’s contents or increasing the assigned memory. For the former, refer to Common Libraries or contact our Support Team for a 1-on-1 session.

Learn more

For the latter, simply click the memory contribution in the Status Bar.

This brings you to the SVH Language Server Arguments Preference where you can change the -Xmx value. In our case, we have changed the assigned memory for the Language Server from lackluster 4GB to a whopping 8GB.

Once you hit the set limit, a notification leading you to the memory settings will pop up.

Improved Autocomplete Performance

You told us, and we listened: Before SVH 2024.2, autocomplete proposals didn’t always appear promptly, interrupting the design flow. For this release, we restructured the internals of the feature so that the list of completion proposals appears much faster. Some of the scenarios reported back to us are now up to 12x faster - an improvement of over 90%.

New CLI Options and Commands

Starting off small, the documentation and compilation-order commands have a new -o <directory> or --out <directory> option to specify where output files will be written to. By default, these used to be written to sigasi-doc in your project’s root.

The star of this release is the addition of the extract command to extract libraries from tools such as Vivado and Quartus or libraries such as UVM and UVVM to a specified path. This allows you to automate the creation of a Library Database.

Finally, we fixed the following issues:

- Added execution permissions to

sigasi-clibinary - Fixed wrong version reported through

-V

[Only in Sigasi Visual HDL Enterprise Edition] Contact our Sales Team for more information.

Quality of Life

- Moved the Enterprise Edition license check for documentation generation to the start instead of the end

- Added a pop-up to open a Sigasi project in a parent folder if none is present in the current folder

- Added a pop-up to create a Sigasi project if none is detected in the current or any parent folders

- Added restoring of Sigasi custom views on reload and restart

- Disabled the find widget in Preferences View, Documentation View, Templates Editor, and Tools and Libraries page pending a fix for a VS Code issue

Further New and Noteworthy

- Added over 30 new SystemVerilog static templates

- Added over 20 new VHDL static templates

- Added a new menu entry to set the top level from the Libraries View

- Added an option to choose where to generate documentation

- Added an

Expand Allbutton to the Libraries View - Added keyboard navigation for the Net Search

- Added more padding to the menu items in the Templates Editor

- Added variable support to autocomplete templates

- Added more validation in the Templates Editor, preventing the creation of corrupt templates

- Moved rename refactoring to the generic

Refactorcontext menu - Moved

Exclude from Buildto context menu of the Sigasi Project View - Added validation of project description files before starting the extension

- Changed required license for Documentation View to Designer Edition

- Improved walkthrough

- Open the release notes on install or update of the plugin

- Expanded

Unsorted associationslinting rule to all constructs supporting associations - Disabled the

Configure library xilinxcorelibQuick Fix as it is superseded by Tools and Libraries - Removed the ability to configure a different installation of Java

- VHDL Cleaned up autocomplete labels

- Verilog Improved labels for typedef enums, unions, and structs

Talkback

- Added events when a license is requested or checked

- Added the product type to every message

Bug Fixes

- Fixed issues with the Talkback server becoming unavailable and incorrectly disabling the license

- Fixed broken Documentation Generation when

Server log levelis set toDebug - Fixed refreshing of view when creating a workspace

- Removed error dialogs when cancelations occur

- Removed error dialogs when toggling Talkback without a license

- An already opened License Page is now focused on clicking the license entry in the status bar

- Scheduled a build after changes to the

Minimal License to Checkout - Fixed incorrect semantic highlighting in rare cases

APPLYbutton in the Templates Editor is now disabled if there are errors in the template- Fixed inability to add and edit templates when there were no custom templates yet in the Templates Editor

- Fixed the version number in generated documentation

- Fixed empty Project Preferences page

- Fixed incorrect application of stuttering setting

- VHDL Redirect to the original

unisim_retarget_VCOMP.vhdinstead ofretarget_VCOMP.vhdwhen the protectedunisim_retarget_VCOMP.vhdpis referenced - VHDL Fixed generics order in the Outline View

- VHDL Fixed missing FSM dead state detection

- VHDL Fixed

Set as Top Levelwhen the matching entity is in a different file - VHDL Fixed missing hover for large physical literal values, e.g,

3333 min - VHDL Fixed false positive “No matching subprogram was found” error for protected type bodies

- VHDL Removed

Add DeclarationQuick Fix from character literals - Verilog Consistently use

Verilog/SystemVerilogto refer to Verilog and/or SystemVerilog - Verilog Fixed recognition of include files starting with a colon character

- Verilog Fixed false positive deprecated macro warnings in disabled preprocessor branches

Upgrade Instructions

The VHDL linting rule 94 was changed from ignored to info. If you see more info issues and would like to revert to the old behavior, you can do so by configuring the severity of the Incomplete port map or generic map: using defaults linting rule to ignore in the Project Preference View.

The libraries extracted in SVH 2024.1 are not compatible with SVH 2024.2. To migrate, rerun the extraction in SVH 2024.2 and synchronize project configuration for libraries. If you have not yet used library extraction or have not used SVH 2024.1, no action is required. Learn more

Upgrading to 2024.2.1

If you previously set the License to check out setting to either Professional or Enterprise, you must

manually toggle the Enable Uvm Linting setting in order to show the UVM linting results again.

Sigasi Visual HDL 2024.2.1 Point Release

On October 15, we released Sigasi Visual HDL 2024.2.1. This release contains the following changes and bug fixes:

- Improved appearance of

Add tool or librarydialog of Tools and Libraries page - Fixed issue where content of packages with the same name was being merged in Libraries View

- Improved VHDL FSM templates

- Added progress visualization and cancelation for Vivado libraries extraction process

- Removed

License To Check Outsetting - Added

Enable UVM Lintingsetting. See upgrade instructions to learn how to use this new setting. - Introduced

Check generics,Check ports, andCheck parametersarguments for VHDL linting rule 164, and rename description. Parameters are not checked by default. - Fixed incorrect exit code of CLI

- Improved categorization of issues in problem reports generated by CLI

- Decode paths in CLI output

- Added

--absoluteoption to the CLIverifycommand to use absolute paths to refer to filenames instead of Sigasi project paths

The enablement of UVM linting rules was overhauled. See our upgrade instructions.

Sigasi Visual HDL 2024.2.2 Point Release

On November 12, we released Sigasi Visual HDL 2024.2.2. This release contains the following changes and bug fixes:

- Fixed Windows issue where CLI did not run when installed on a different drive or network drive

- Added better feedback when enabling UVM linting

- Fixed rendering of blockquotes in our tutorials

- Fixed editing of files that were linked to Common Libraries while being open

- Modified the Heap Size Visualization status contribution to display the used memory instead of the maximum available memory

- Fixed server shutdowns on machines with limited resources

- Fixed invalidating of all licenses requiring an up-to-date version

- Added an anonymous identifier to Talkback message to identify messages coming from the same user

- Reenabled the find widget in Preferences View, Documentation View, Templates Editor, and Tools and Libraries page after a fix was provided for a VS Code issue . We recommend upgrading to VS Code version 1.95 which provides this fix.

Update or Install

You can download a .vsix file and manually install it in VS Code.

- Linux: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-linux.vsix

- Windows: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-win32.vsix

The SHA sum is downloadable from https://download.sigasi.com/vs-code/updates/latest/vs-code-sha1.txt .

System Requirements

Sigasi Visual HDL requires:

- Windows 10 or Windows 11 64-bit

- Red Hat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.77 and < 2.0

We recommend having at least 8GB of memory and about 1GB of free disk space available for Sigasi Visual HDL. For the best experience, we also recommend to always use the latest release of VS Code.

Feedback

We welcome your feedback through the usual channels or the comments below. Note that we clear the comments on this page after each official release.

Transition Information

For our loyal legacy users:

If you are already using VS Code, the transition to SVH should be completely transparent. Your existing projects and licenses will just work.

If you are using Eclipse, we do not want to leave you hanging. You could transition to VS Code right away with your existing projects and licenses, but if you want a little more time, then we have got you covered with Sigasi Visual HDL in Eclipse. We will start ramping down support for Eclipse in 2025. For information specific to using SVH in Eclipse, as well as who to talk to about your transition, please check these release notes.