Sigasi® Visual HDL™ (SVH™) 2025.2 features the new Sigasi View, improvements to license management, state machine visualization and case statement linting, multi-file formatting for the CLI, as well as compilation recipe exports and tool-driven Sigasi projects. See the highlights below.

TL;DR

The overarching theme for this release is adapting to your setup, ensuring SVH fits seamlessly into your design flow. Additionally, we implemented numerous enhancements to state machines and case statements in VHDL.

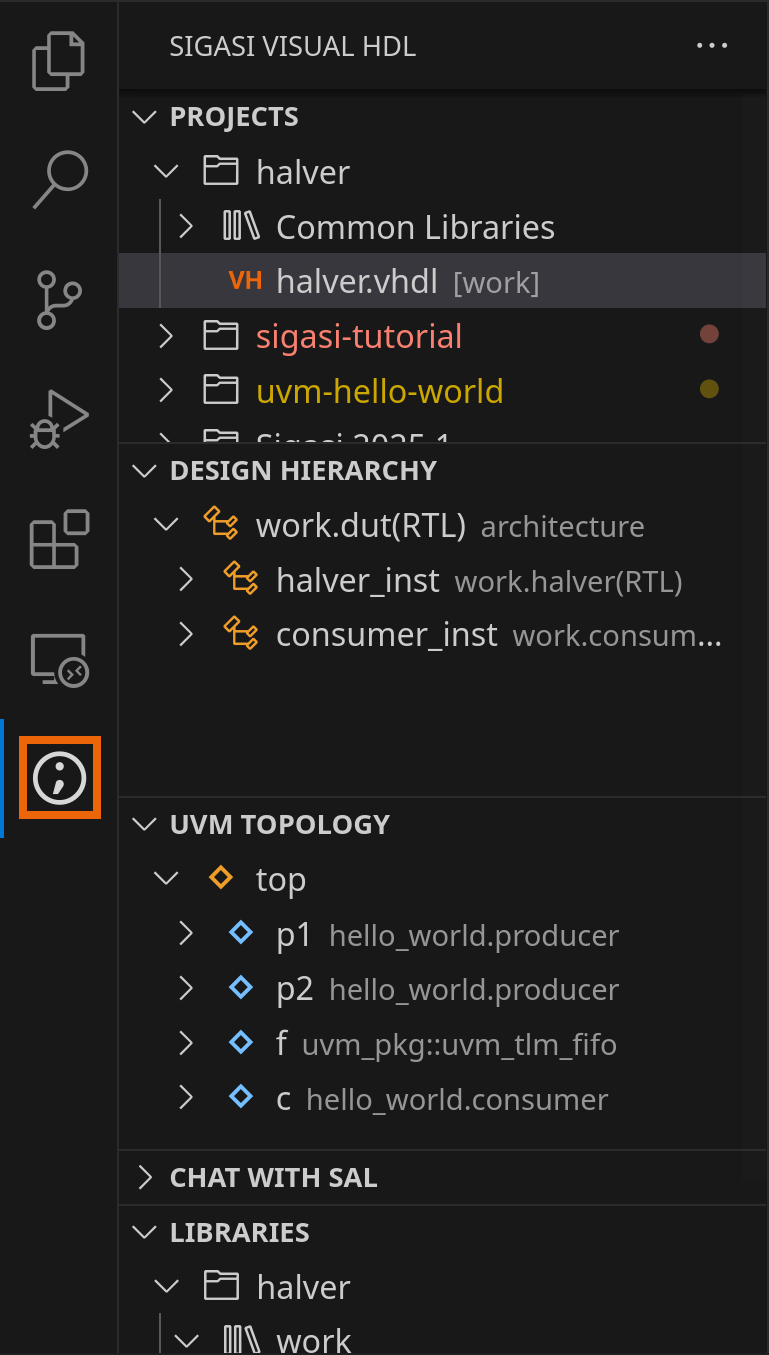

To declutter the Explorer Sidebar, SVH 2025.2 groups its views into a comprehensive Sigasi View for all activities specific for hardware design.

To enable efficient license usage, you can now manually downgrade a license to make room for your colleagues.

For VHDL, powerful new features will transform how you design state machines in SVH, making you more productive and confident. The State Machines View receives additional visualizations for dead states, unresolved states, reset transitions, and it shows constant state names in the diagram where possible. The case statement completeness linting rules were expanded to match many new patterns.

Also for VHDL, the Sigasi CLI can now format multiple files in one command, minimizing the overhead of launching the CLI separately for every file.

As a small improvement for those working often with read-only files, we now show a preview when user actions attempt to modify these files.

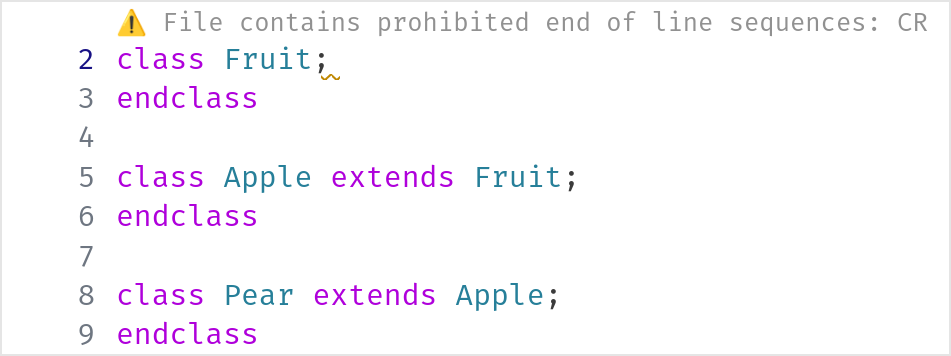

Gremlins no more: the introduction of a new linting rule allows you to prohibit non-conforming end of line sequences.

Furthermore, to fit the SVH platform seamlessly into your design flow, you can now use SVH to either drive your downstream tools through the Compilation Recipe, or let tools such as VCS and Questa configure the new Sigasi projects. These allow you to reuse your existing tools, compilation scripts, and design flows, liberating you from the need to duplicate the project in yet another platform.

As a cherry on top, this release includes over 40 bug fixes and miscellaneous improvements.

Sigasi View

We have grouped all of SVH’s views into the Sigasi Sidebar, indicated by the icon in the activity bar. This ensures the Explorer View remains clutter-free, even when you have many extensions installed.

Do you prefer the old style?

Simply drag and drop the SVH icon onto the Explorer, or the drag the Explorer icon between the Sigasi views.

Where is the Outline?

The Outline will still be in the Explorer View, we recommend you pin it to the secondary sidebar.

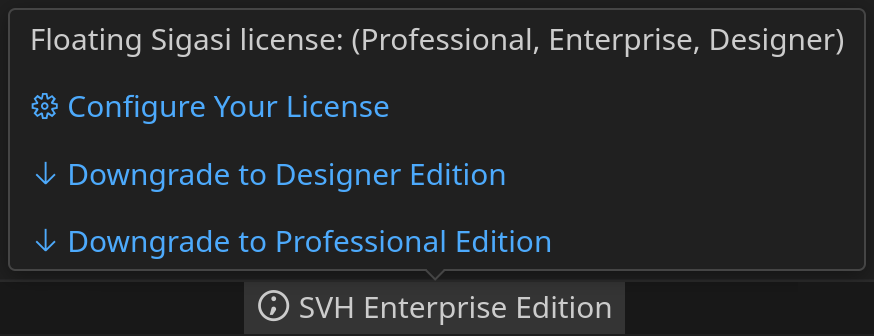

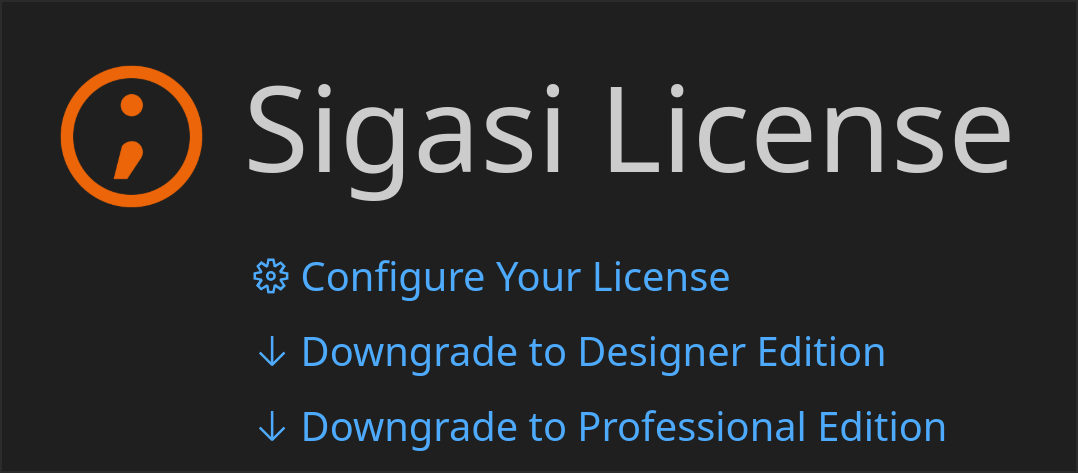

License Downgrade

As a team, you usually have a mix of licenses, some Enterprise, a few Professional, and the rest Designer. To allow you to share your licenses more efficiently, you can manually downgrade your license by hovering over the status bar item. The license will automatically be upgraded again when you use a feature that requires it.

Learn more

Alternatively, the option is presented on the license configuration page.

Prohibited End of Line Sequences

Prohibited end of line sequences

They are easy to introduce, but much harder to spot: non-conforming end of line sequences! Some end of line sequences confuse tooling, so by default, SVH 2025.2 warns when simple carriage returns (CR) are used as end of line sequence.VHDL State Machine Visualizations

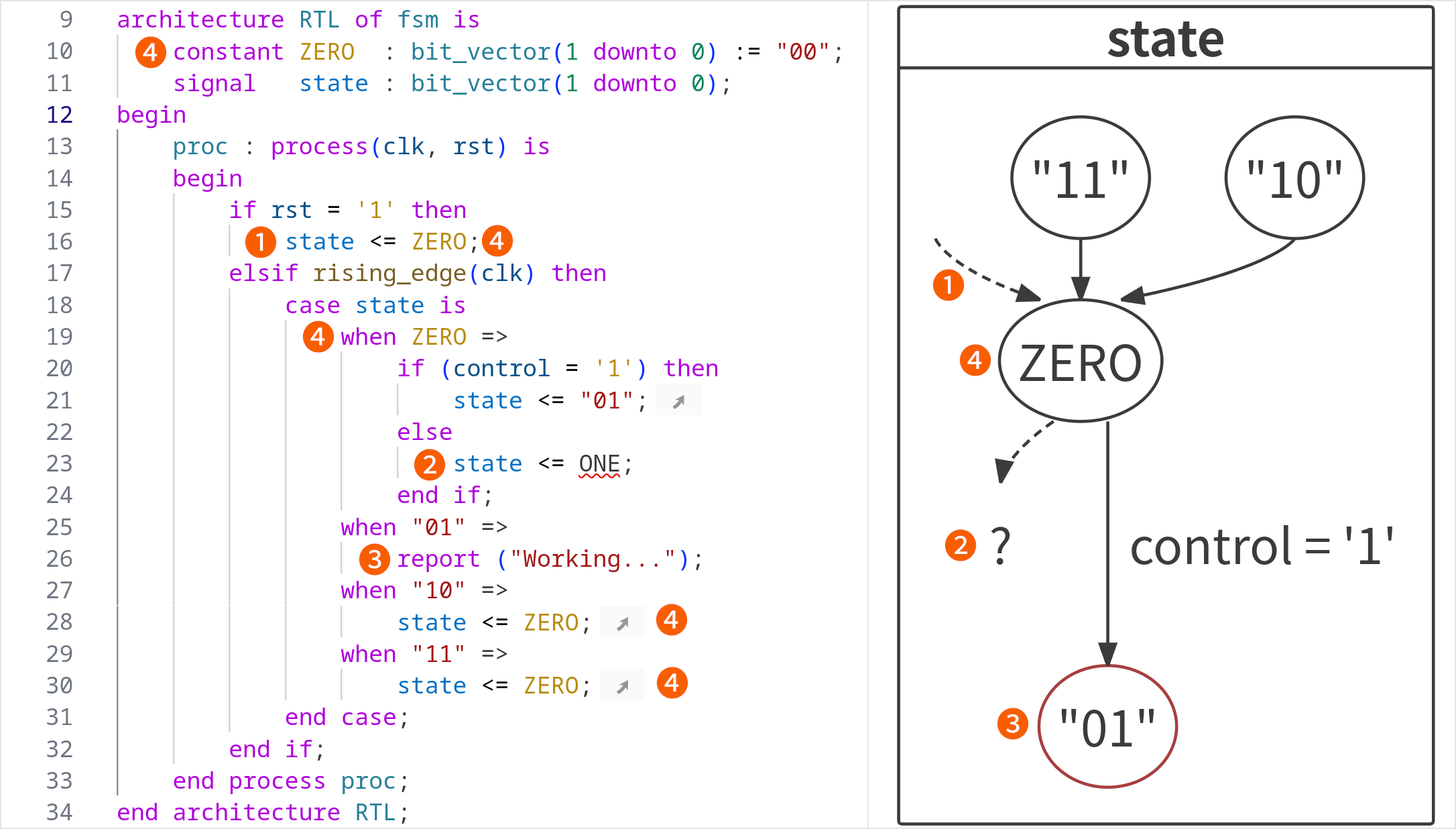

There are four new visualizations for the State Machines View that will save you lots of trouble when debugging your state machines.

- Reset state (dashed arrow): States that are set in the reset block

- Unresolved state (dashed arrow to a

?): SVH found a state transition but cannot determine the end state - Dead state (red outline): States that have incoming transitions but no outgoing

- State names: When consistently using constants their names will be displayed instead of their value

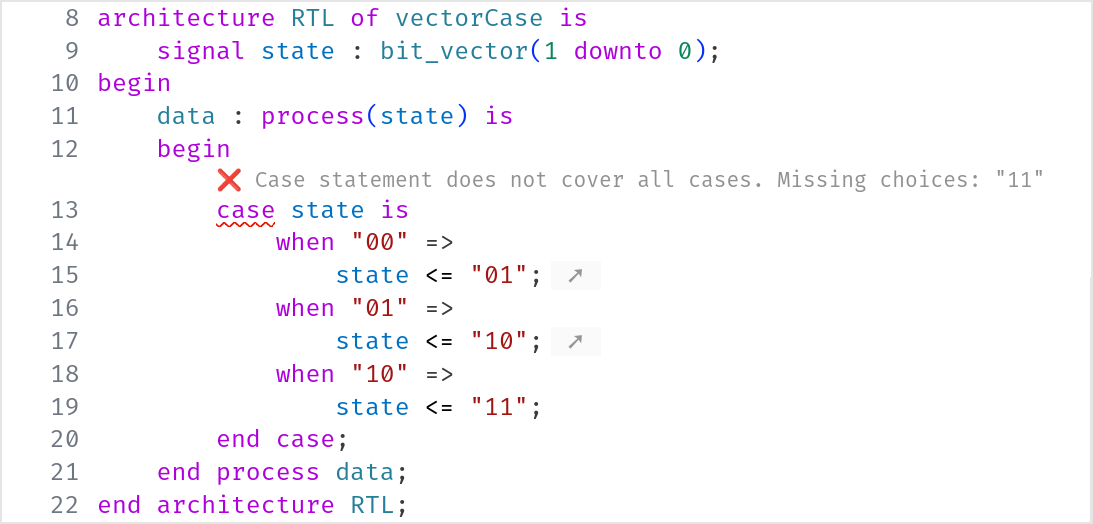

VHDL Case Statements

You will notice that linting rules, inlay hints, and state machine analyses are more consistent, work on more cases and generally act as expected much more often. Specifically, they should now treat case (generate) and select statements equally. Additionally, vector and integer support was added. The navigation from the State Machines View was significantly improved, too.

Some smaller improvements include:

- Added a Quick Fix for

Cannot combine 'others' with other choices - Added a Quick Fix for Consistent use of ‘others’ in case statements

- Made Consistent use of ‘others’ in case statements linting rule configurable

- Fixed missing transitions for vectors spread over multiple case statements

- Fixed case testing against alias states

- Fixed missing Inlay Hints for specific states without outgoing transitions

- Added handling of

state <= (others => '0')aggregates

Linting Rules

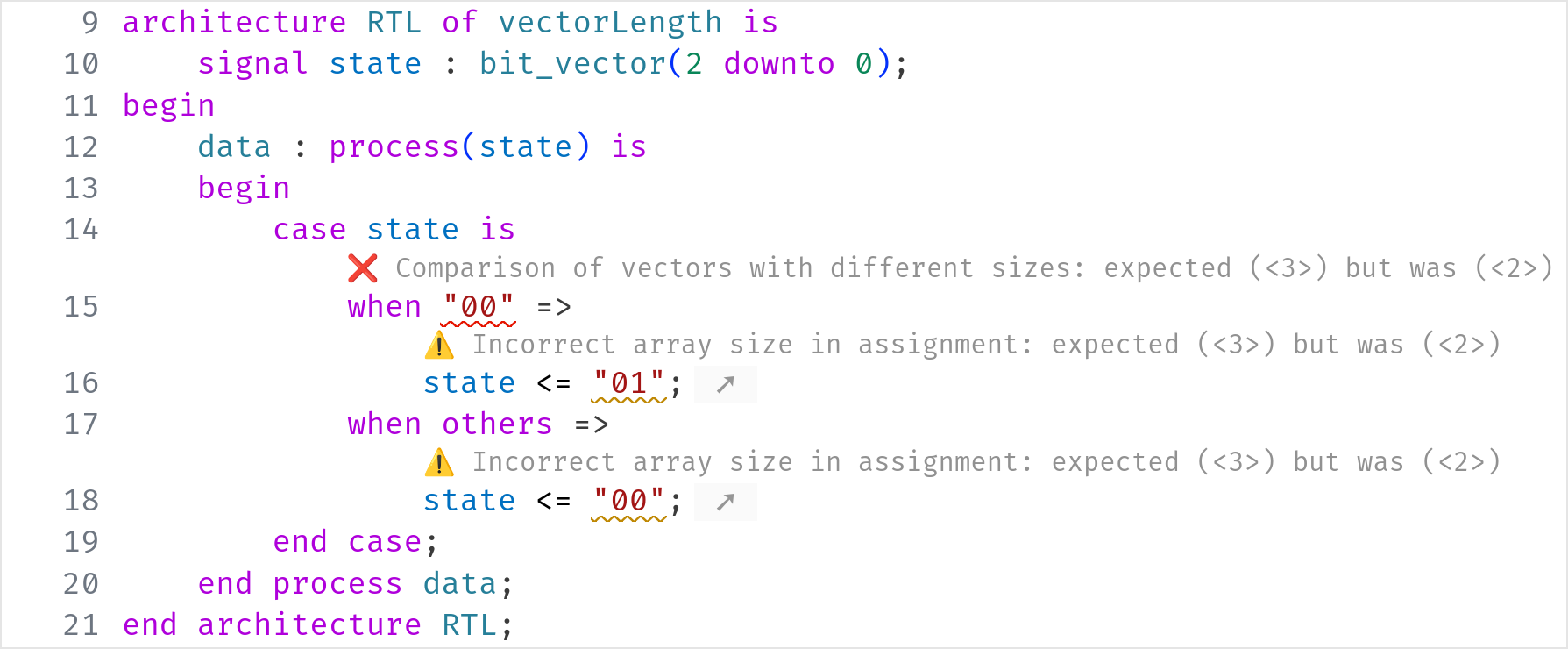

Comparison of vectors with different sizes

SVH 2025.2 introduces a rule that marks comparisons of vectors with different sizes.

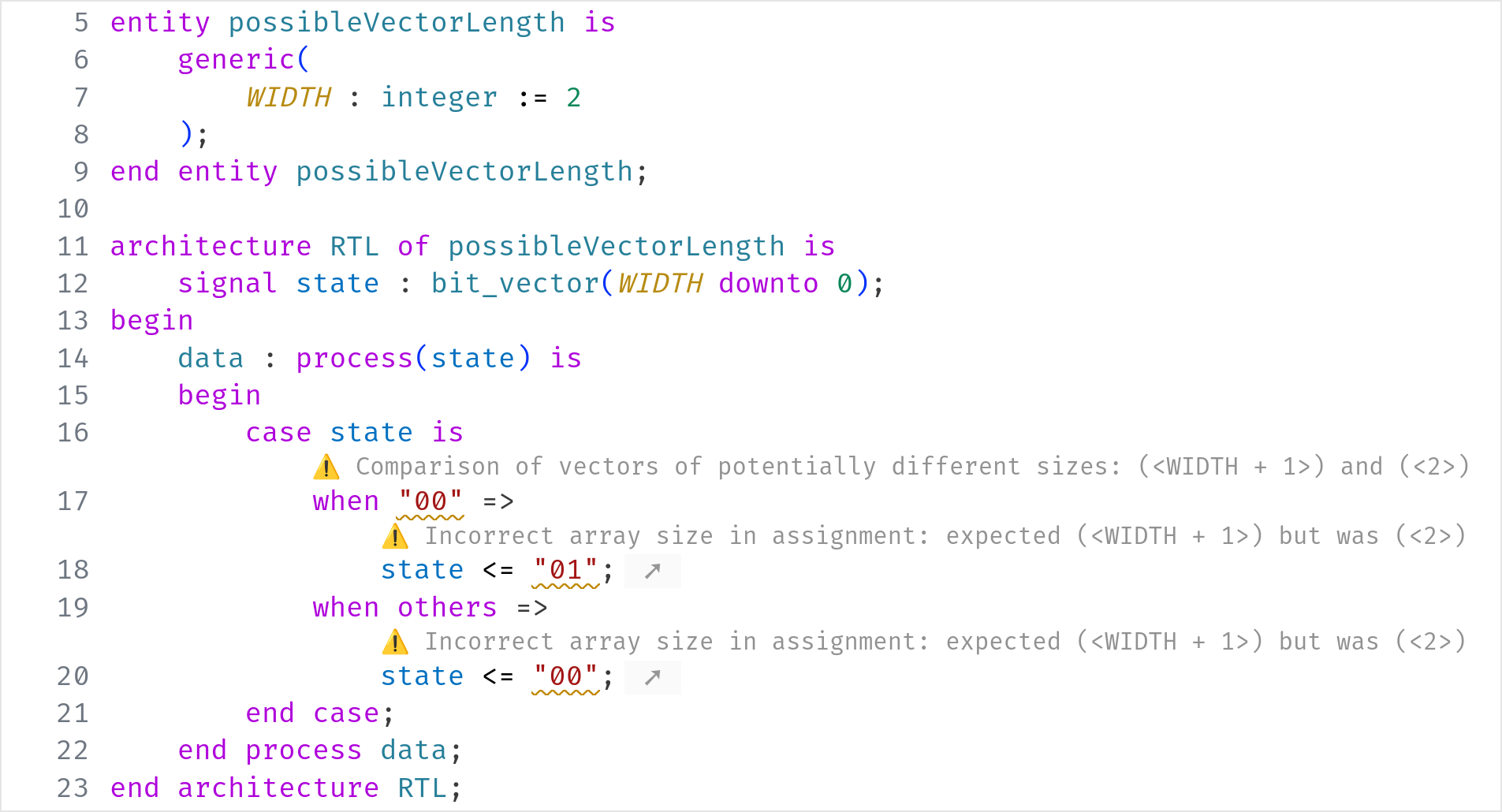

Learn moreComparison of vectors with possibly different sizes

Similar to the previous rule, but now with generics. When these are used, the signal that is tested (state) should also use the generic to be correct in all cases.

Vector & integer case statement completeness

As an enhancement of the existing case statement completeness linting rules, case (generate) and select statements now support vectors and integers.Sigasi CLI

The CLI format command can now process multiple VHDL files in a single invocation.

This significantly speeds up formatting a sequence of files, as it needs to initialize the CLI only once.

This is especially useful in combination with the parameter expansion of your Linux shells,

allowing commands such as sigasi-cli format path/to/project/**/*.vhd{,l} in Bash or Zsh.

Learn more

We also added the list-targets and verify-target-commands commands to list and verify the experimental Sigasi Project target commands.

Learn more: list-targets

Learn more: verify-target-commands

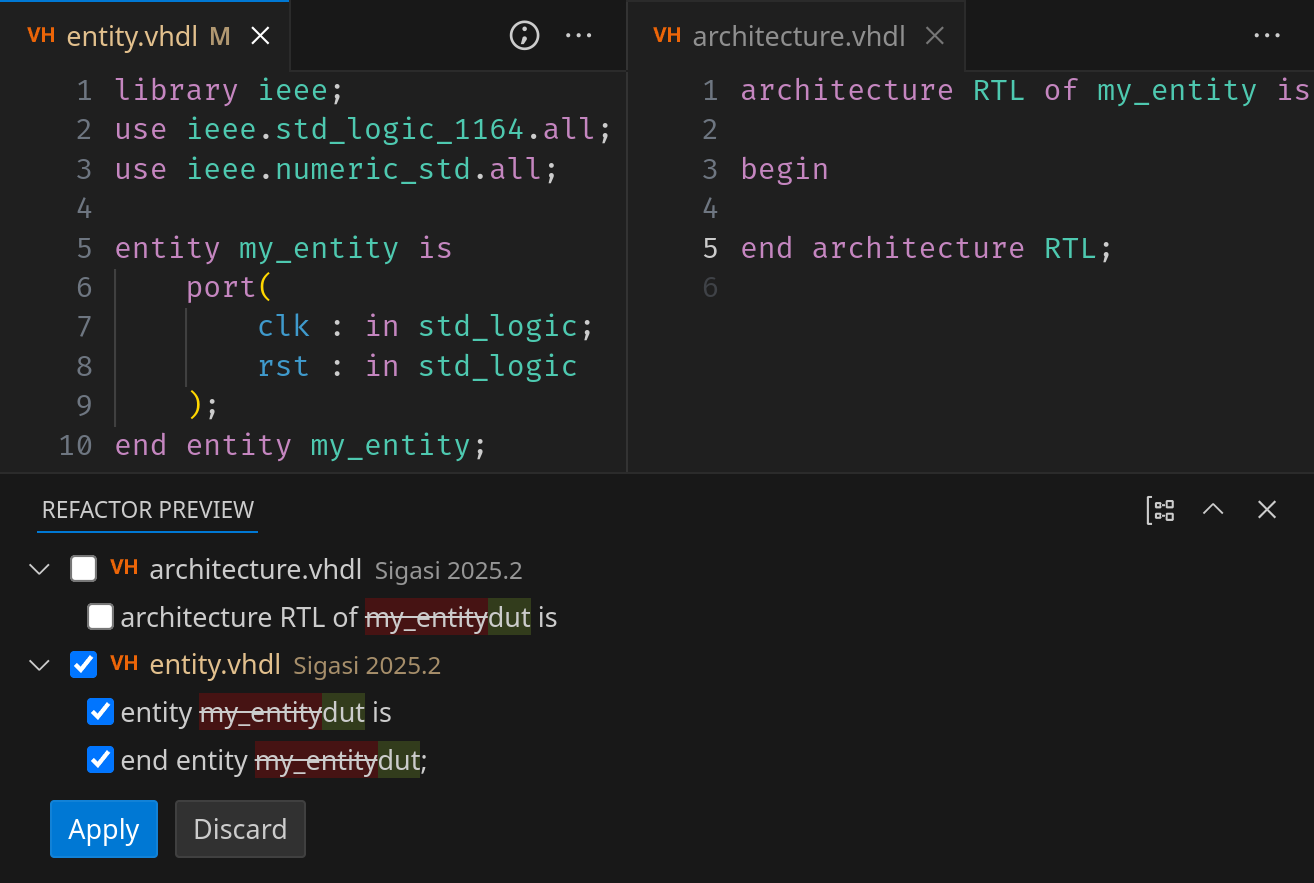

Read-Only Preview

When a Quick Fix or a rename action affects a read-only file, a preview will automatically be shown. In this preview, changes to read-only files are shown, but not selected by default, ensuring that they will not be applied unless explicitly confirmed.

For example, architecture.vhdl below is read-only. When we try to rename my_entity to dut, the preview is automatically triggered.

You can disable this preview behavior by toggling the

Learn more

Experimental Features

The following new features are open to everyone, but disabled by default because they are experimental. If you do give them a try, please contact us with your findings, troubles, and suggestions.

Compilation Recipe

Tired of adjusting your project definition in every tool after making a change in SVH? Make SVH the cockpit of your design flow instead. By exporting the Compilation Recipe JSON straight from SVH or the CLI, you have all the details at hand to drive tools further in the flow. The recipe includes the complete compilation order, Verilog initial defines and include paths, language levels, libraries, and more.

You can generate the compilation recipe in SVH via the Sigasi: Export Compilation Recipe command or via the CLI using sigasi-cli compilation-recipe path/to/project.

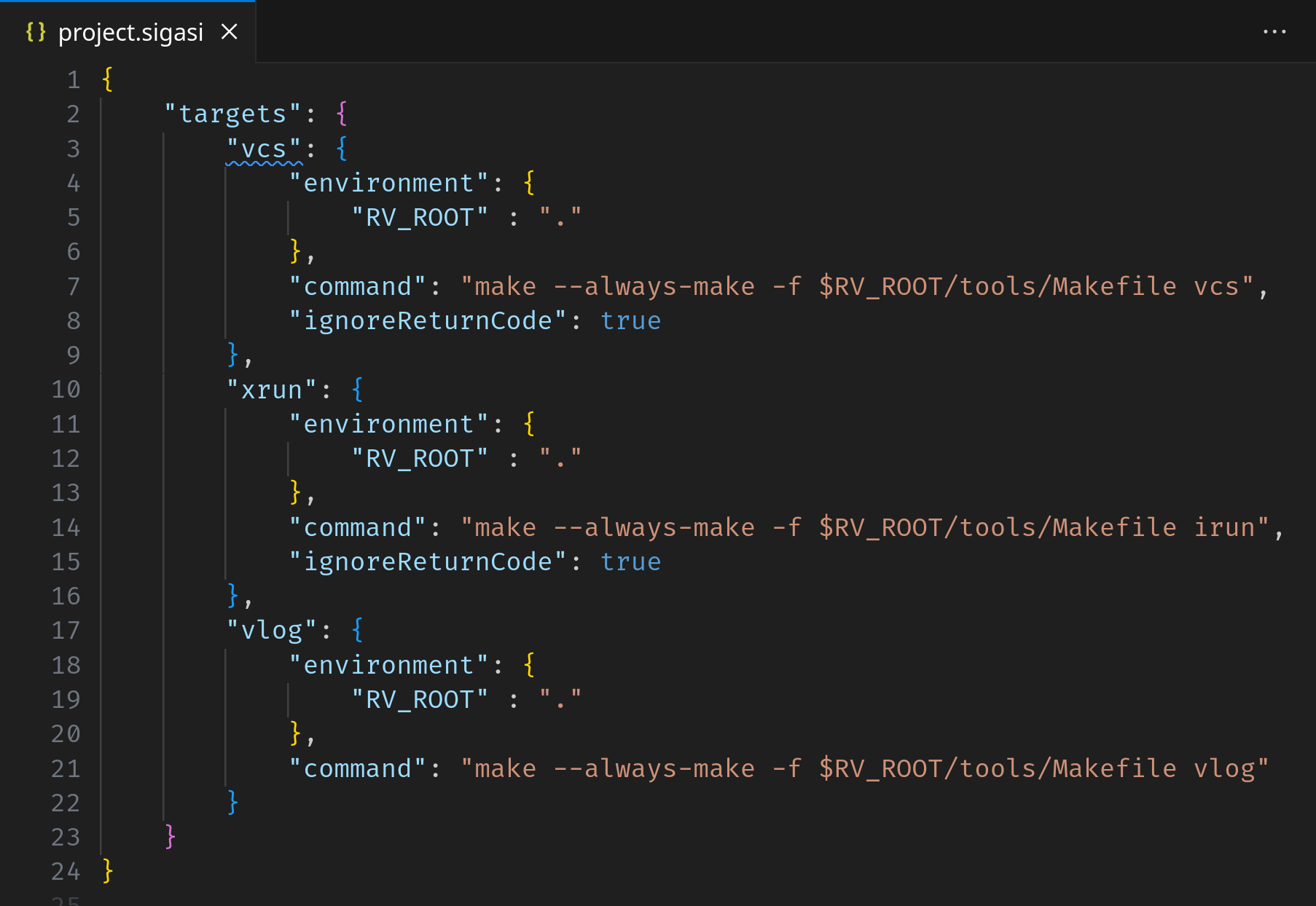

Sigasi Projects

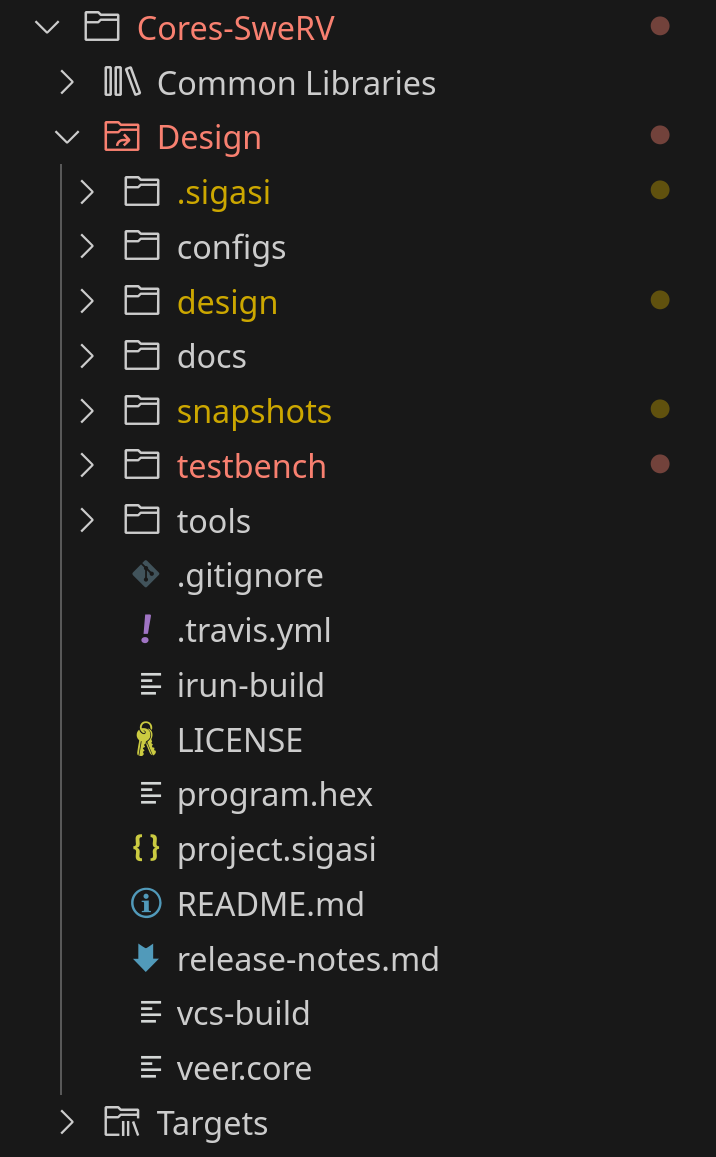

Teased in the previous release—and available for the wider public now—Sigasi projects are powerful new projects that allow you to reuse your existing project descriptions to configure SVH. You can enable the feature through the

project.sigasi file. The editor will help you to write the JSON file through autocompletes and hovers.

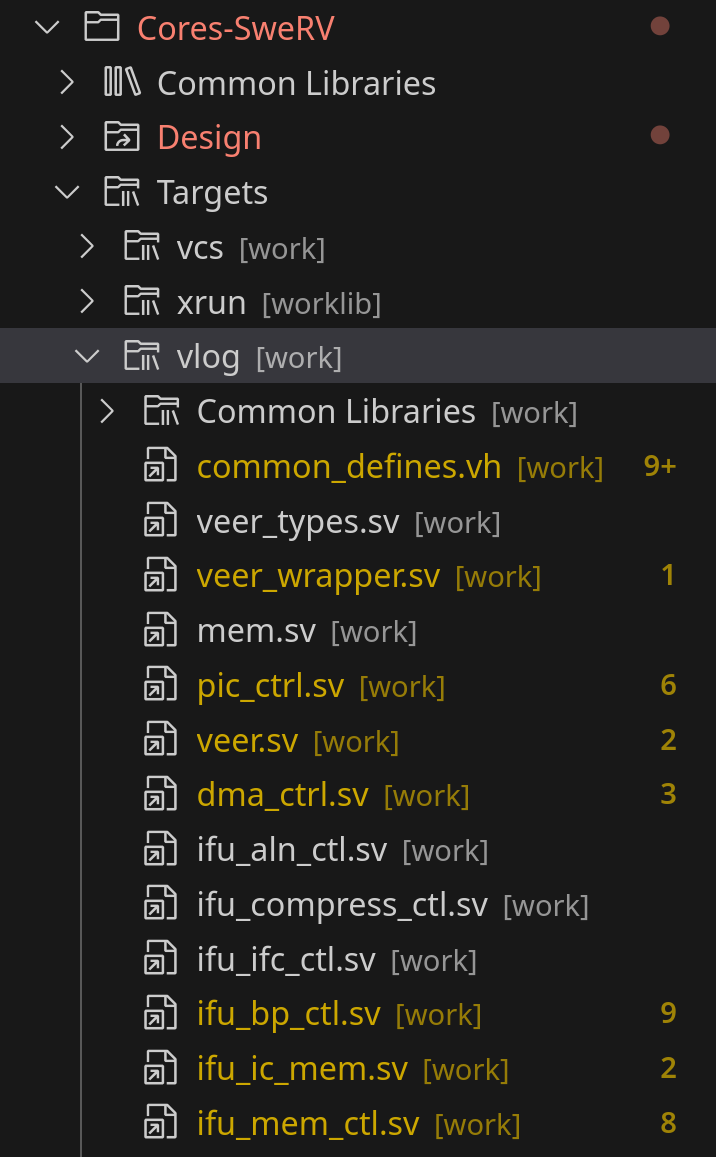

This example contains three targets, for three different tools. A target requires a command and an environment. Simply fill in your build command and its required environment, and watch the magic happen. In the background, process stubs and a prepared shell environment analyze which files are passed to your simulators and compilers. Using those, SVH replicates the project definition used by your favorite tool.

You can see the full project as it is defined on disk in the Design node in the Sigasi Projects View.

However, if you would like to see the compilation order per target, you can use the Targets node.

This new project setup makes integrating an existing project trivial.

Learn more

Quality of Life

- SVH now scans deeper, looking for HDL files when it does not see a Sigasi project. This way, the project creation pop-up will be shown more often.

- Enabled hovers in the Preprocessor View

- Open the first panel by default in the Project Settings

- Decreased redundant rerenders of State Machine Diagrams

Further New and Noteworthy

- Added support for carriage return newlines (

\r) - Added duplicate template reporting in the Templates Editor

- Open file explorer on the current Library Database path when changing the path

- Enabled the Sigasi Editor Actions for Common Libraries files

- Enabled selection for colored nodes in State Machines

- Removed redundant license setup pop-up

- New projects no longer map the project to work

- Improved legibility of our wordmark logo

- Added a

Configure Your Licensebutton on hover over the license status bar item - Verilog Added support for ternary operators in always blocks

- Verilog The

`protectand`endprotectVerilog preprocessor directives are now ignored - Verilog Added support for Cadence’s

//pragma protect ...encryption comments - VHDL Enabled Incorrect vector range direction for paths, e.g.,

work.pkg.list - VHDL Added formatting alignment on

:for attributes

Bug Fixes

- Fixed string parsing in autocomplete templates

- Fixed reporting following the Sigasi: Import Eclipse Templates command

- Fixed small typos in the settings page

- Fixed grayed out

APPLYbutton on subsequent edits in Templates Editor - Fixed order of warning and info boxes on the settings pages

- Fixed missing refresh on diagram views after acquiring a Professional license

- Fixed rare case that would prevent builds

- Fixed bug preventing license release on CLI finish

- Ensured consistent order in the CLI’s

--help - Verilog Fixed false positive errors when using elaboration system tasks, e.g.,

$erroror$warning - Verilog Fixed Preprocessor View hovers for diff views

- Verilog Removed redundant

Open instantationcontext menu item in the UVM Topology View - Verilog Fixed error rendering for include paths in the project settings

- Verilog Fixed false positive End name not allowed without begin name error

- Verilog Fixed false positive Multiple statements per line warning for multiple assignments

- Verilog Fixed hover content on statements under an include directive

- Verilog Minor adjustments were made to the preprocessor to improve inclusion loop detection

Updates

- Moved all SVH views to the Sigasi View

- VHDL Renamed

Case alternative contains redundant choiceslinting rule toCannot combine 'others' with other choices - VHDL Renamed Case statement contains all choices explicitly. You can safely remove the redundant ‘others’ linting rule to

Consistent use of 'others' in case statements - Updated to Chromium 116 from 106 for faster diagram generation

Update or Install

If you have downloaded SVH from the VS Code Marketplace , your installation will automatically update.

You can also download the latest .vsix file and manually install it in VS Code.

- Linux: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-linux.vsix

- Windows: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-win32.vsix

The SHA sum is downloadable from https://download.sigasi.com/vs-code/updates/latest/vs-code-sha1.txt .

System Requirements

Sigasi Visual HDL requires:

- Windows 10 or Windows 11 64-bit

- Red Hat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.80 and < 2.0

We recommend having at least 8 GB of memory and about 1 GB of free disk space available for Sigasi Visual HDL.

Feedback

Our Support Team happily welcomes any of your feedback.

Transition Information

You can transition to VS Code right away with your existing projects and licenses, but if you want a little more time, we have you covered with Sigasi Visual HDL in Eclipse.

We will start ramping down support for Eclipse in 2025. Please check these release notes for information specific to using SVH in Eclipse and whom to talk to about your transition.