Please note that we will start ramping down support for Eclipse during 2025 to focus exclusively on VS Code for your benefit. Please enjoy and do get in touch with either our Sales Team or Support Team if you need any help transitioning to VS Code.

TL;DR

The SVH 2025.2 for Eclipse release brings over 25 bug fixes and improvements and modernizes the technology stack used.

Java 21 is now the minimum required JRE version, up from 17.

Ensure yoursigasi.ini’s-vmflag points to a Java 21 JRE.

For VHDL, powerful new features will transform how you design state machines in SVH, making you more productive and confident. The State Machines View receives additional visualizations for dead states, unresolved states, reset transitions, and it shows constant state names in the diagram where possible. The case statement completeness linting rules were expanded to match many new patterns.

Gremlins no more: the introduction of a new linting rule allows you to prohibit non-conforming end of line sequences.

Prohibited End of Line Sequences

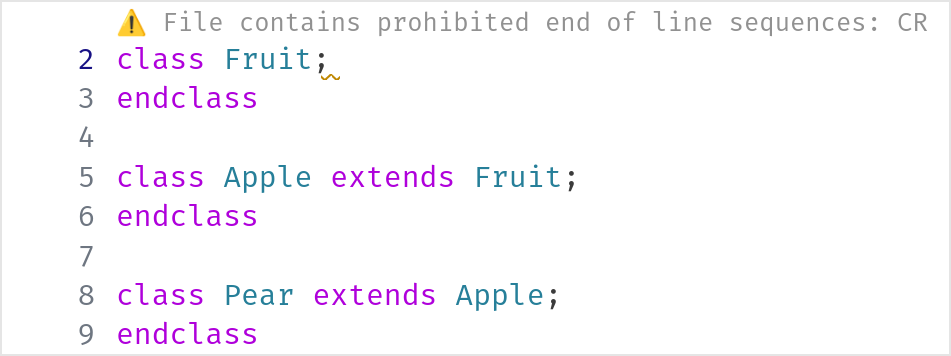

Prohibited end of line sequences

They are easy to introduce, but much harder to spot: non-conforming end of line sequences! Some end of line sequences confuse tooling, so by default, SVH 2025.2 warns when simple carriage returns (CR) are used as end of line sequence.VHDL State Machine Visualizations

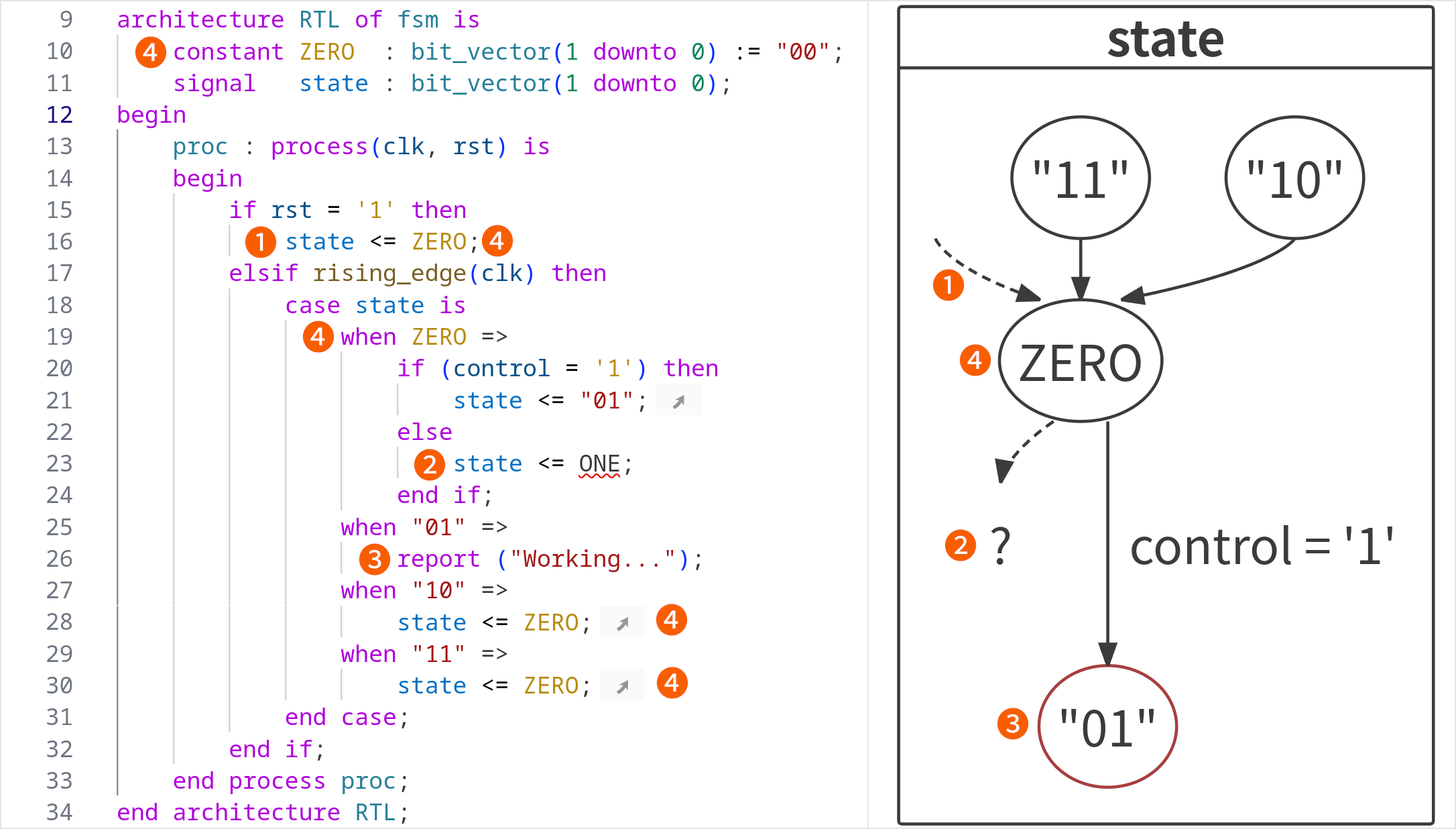

There are four new visualizations for the State Machines View that will save you lots of trouble when debugging your state machines.

- Reset state (dashed arrow): States that are set in the reset block

- Unresolved state (dashed arrow to a

?): SVH found a state transition but cannot determine the end state - Dead state (red outline): States that have incoming transitions but no outgoing

- State names: When consistently using constants their names will be displayed instead of their value

VHDL Case Statements

You will notice that linting rules, inlay hints, and state machine analyses are more consistent, work on more cases and generally act as expected much more often. Specifically, they should now treat case (generate) and select statements equally. Additionally, vector and integer support was added. The navigation from the State Machines View was significantly improved, too.

Some smaller improvements include:

- Added a Quick Fix for

Cannot combine 'others' with other choices - Added a Quick Fix for Consistent use of ‘others’ in case statements

- Made Consistent use of ‘others’ in case statements linting rule configurable

- Fixed missing transitions for vectors spread over multiple case statements

- Fixed case testing against alias states

- Added handling of

state <= (others => '0')aggregates

Linting Rules

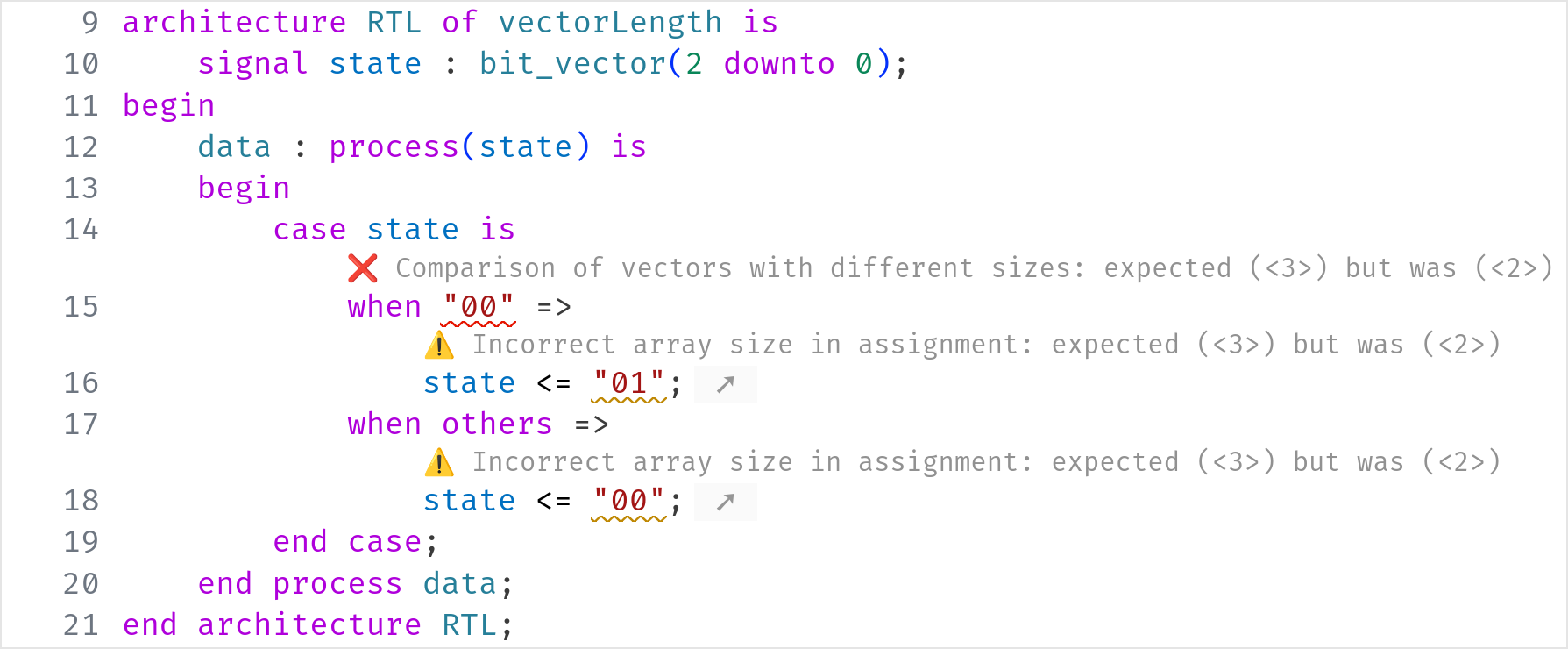

Comparison of vectors with different sizes

SVH 2025.2 introduces a rule that marks comparisons of vectors with different sizes.

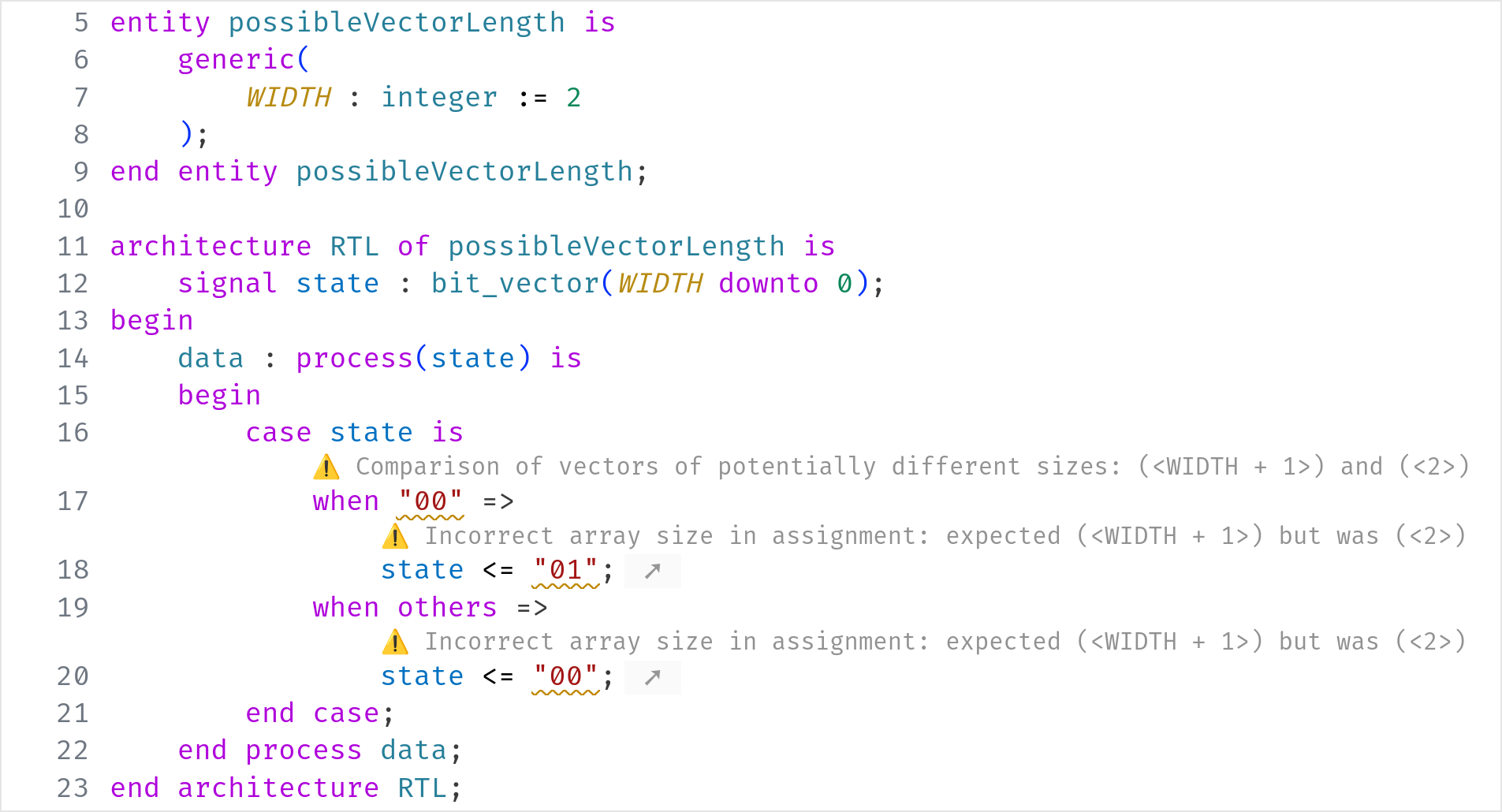

Learn moreComparison of vectors with possibly different sizes

Similar to the previous rule, but now with generics. When these are used, the signal that is tested (state) should also use the generic to be correct in all cases.

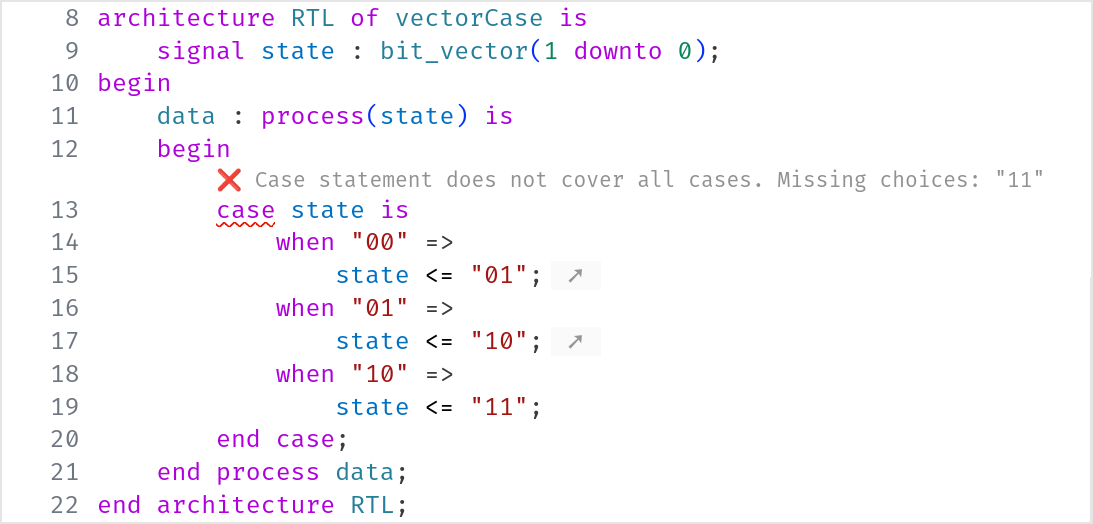

Vector & integer case statement completeness

As an enhancement of the existing case statement completeness linting rules, case (generate) and select statements now support vectors and integers.New and Noteworthy

- Made language version selection text consistent

- Added support for carriage return newlines (

\r) - Enabled selection for colored nodes in State Machines

- Improved legibility of our wordmark logo

- Verilog Added support for ternary operators in always blocks

- Verilog The

`protectand`endprotectVerilog preprocessor directives are now ignored - Verilog Added support for Cadence’s

//pragma protect ...encryption comments - VHDL Enabled Incorrect vector range direction for paths, e.g.,

work.pkg.list - VHDL Added formatting alignment on

:for attributes

Bug Fixes

- Fixed rare case that would prevent builds

- Verilog Fixed false positive errors when using for elaboration system tasks, e.g.,

$erroror$warning - Verilog Fixed false positive End name not allowed without begin name error

- Verilog Fixed false positive Multiple statements per line warning for multiple assignments

- Verilog Removed redundant

Open instantationcontext menu item in the UVM Topology View - Verilog Fixed hover content on statements under an include directive

- Verilog Minor adjustments were made to the preprocessor to improve inclusion loop detection

Updates

- VHDL Renamed

Case alternative contains redundant choiceslinting rule toCannot combine 'others' with other choices - VHDL Changed

Cannot combine 'others' with other choiceslinting rule to error from warning - VHDL Renamed Case statement contains all choices explicitly. You can safely remove the redundant ‘others’ linting rule to

Consistent use of 'others' in case statements - Updated to Chromium 116 from 106 for faster diagram generation and rendering

Sigasi Visual HDL 2025.2.1 Point Release

On July 1, we released Sigasi Visual HDL 2025.2.1. This release contains the following changes and bug fixes:

- Improved handling of possible library database paths in dependencies search paths

- Prevent extracting libraries that are located inside the library database

- Verilog Fixed autocomplete issue for modules with imports

- Verilog Added

Non-standard implicit type conversionlinting rule for type conversions that are not allowed by the LRM, but are supported by several tools - VHDL Changed description of

Consistent use of 'others' in case statementstoMissing or redundant 'others' in case statements

Sigasi Visual HDL 2025.2.2 Point Release

On July 3, we released Sigasi Visual HDL 2025.2.2. This release contains the following changes and bug fixes:

- Fixed installation issue in Eclipse 2023-03 & 2025-06

Sigasi Visual HDL 2025.2.3 Point Release

On July 9, we released Sigasi Visual HDL 2025.2.3. This release contains no relevant changes for SVH in Eclipse.

Sigasi Visual HDL 2025.2.4 Point Release

On July 12, we released Sigasi Visual HDL 2025.2.4. This release contains the following changes and bug fixes:

- Fixed stale warnings and errors

Update or Install

You can download the latest stand-alone version below:

- Linux: https://download.sigasi.com/eclipse/updates/latest/com.sigasi.hdt.product-linux.gtk.x86_64.zip

- Windows: https://download.sigasi.com/eclipse/updates/latest/com.sigasi.hdt.product-win32.win32.x86_64.zip

You can also update automatically when setting :

https://download.sigasi.com/sigasi-studio/updates/composite/

SHA sums (more info ) can be checked via https://download.sigasi.com/eclipse/updates/latest/eclipse-sha1.txt .

System Requirements

Sigasi Visual HDL in Eclipse requires:

- Windows 10 or Windows 11 64-bit

- Red Hat Enterprise Linux RHEL 8 or 9 64-bit

- Sigasi Visual HDL depends on

libXss.so, which is obtainable by installinglibXScrnSaver - Sigasi Visual HDL depends on

webkit2gtk4.0, which is installable through your package manager of choice - You can find more information on supported Linux Operating Systems on the Eclipse website

- Sigasi Visual HDL depends on

Sigasi Visual HDL as a plugin in your existing Eclipse installation requires:

- Eclipse IDE 2023-03 up to and including Eclipse IDE 2025-06

- Java JRE 21

We recommend having at least 8 GB of memory and about 1 GB of free disk space available for Sigasi Visual HDL.

Feedback

Our Support Team happily welcomes any of your feedback.