Sigasi Visual HDL™ (SVH™) 2025.3 features external compiler support & VUnit integration, automatically exports compilation recipe, introduces a state machine transitions table, previews Sigasi projects, offers better library mapping guidance, and embeds the Sigasi CLI in SVH.

TL;DR

This release greatly improves SVH’s ability to integrate into your design flow.

Design flow automation minimizes context switching, optimizing your workflow and saving time. It allows you to automatically run external compilers—such as Questa or Riviera—whenever design files are changed. If you are using VUnit, you can smoothly automate the compilation of your testbench and the population of VS Code’s test view. Finally, you can automatically export the compilation recipe to keep your downstream tools in sync with the changes made in Sigasi.

The new Transitions Table is great for large state machines, where conditions and comments clutter the diagram making it difficult to comprehend. It enables intuitive navigation between your code and the diagram.

Sigasi projects are the pinnacle of integration. If you already defined your project in a tool such as VCS or Questa, you can easily use that definition in a Sigasi Project with scripted targets and have it remain up-to-date without any additional work. If you are starting a new project from scratch, you should consider Sigasi projects with manual targets. These are optimized for integrating existing IP and sharing settings to guarantee compliance with company-wide design rules.

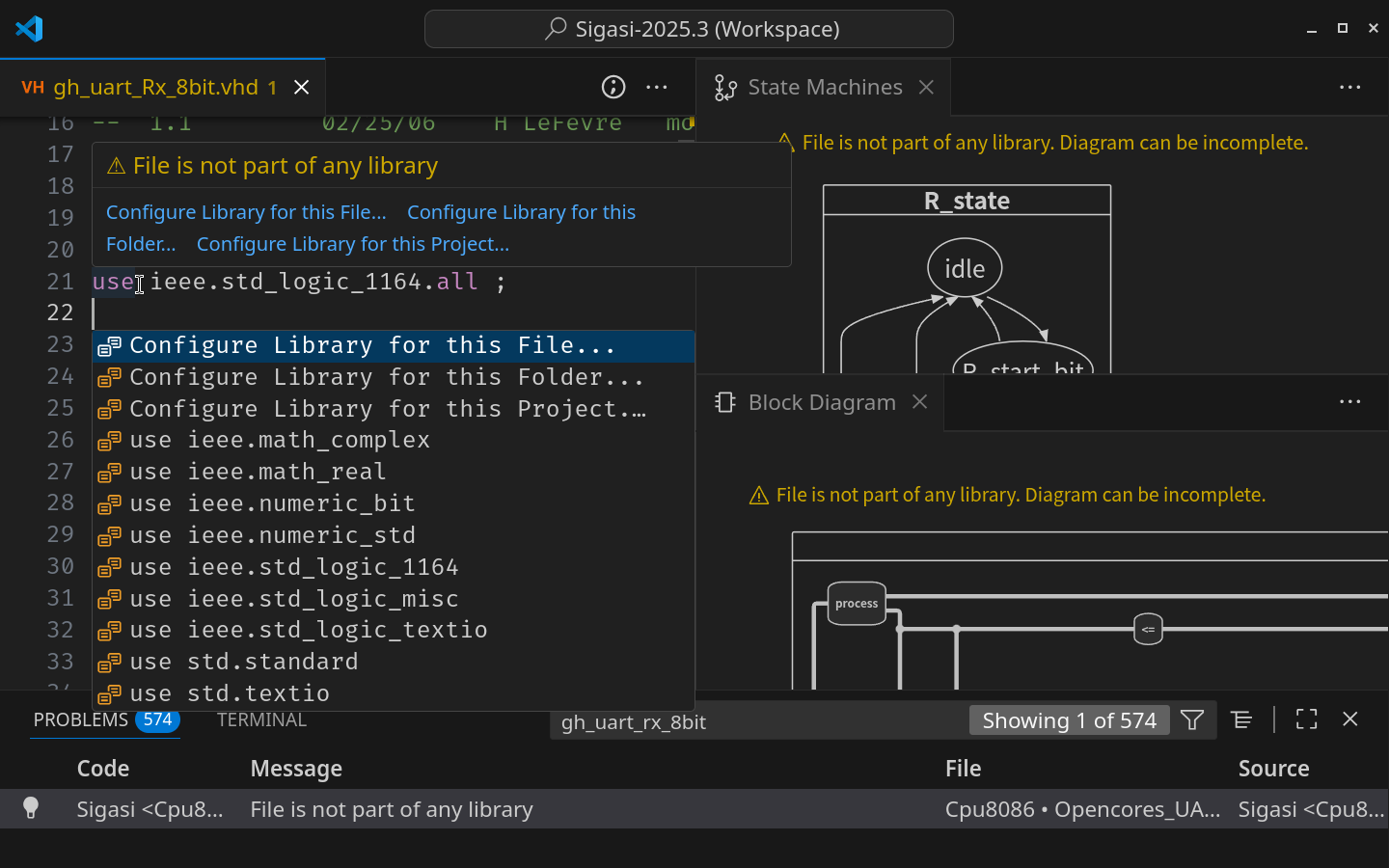

To get the best out of SVH, we advise you to spend some time setting up your project correctly. To guide you towards a stronger project setup, we added many hints when working with files that are not part of the project yet.

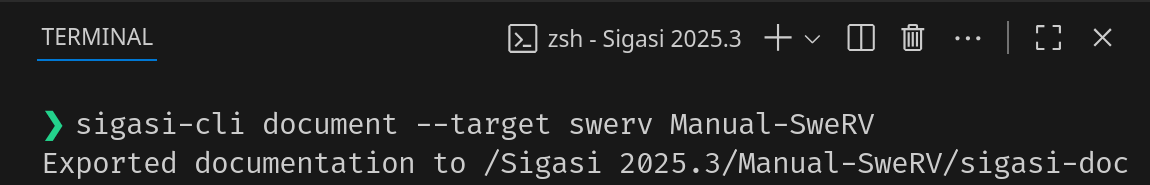

Finally, the Sigasi CLI is now shipped as part of SVH. You can directly access it from the terminal in VS Code.

As a cherry on top, this release includes an extraordinary 75 bug fixes and miscellaneous improvements.

Design Flow Automation

SVH 2025.3 introduces three ways to automate your design flow, minimizing context switches and manual actions, effectively turning SVH into the cockpit of your design.

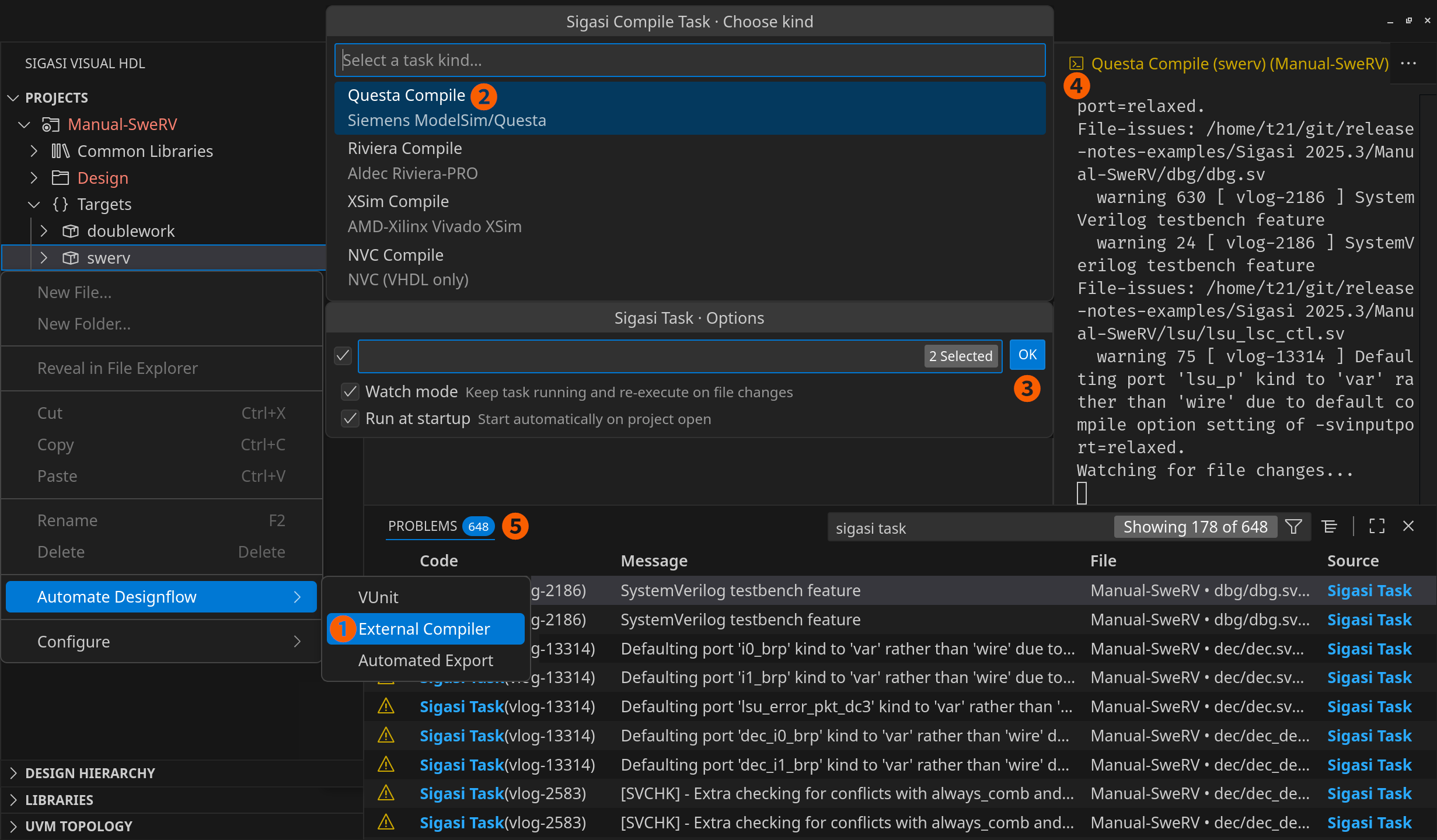

External Compiler Integration

While Sigasi’s linting is excellent at catching many errors early in the design flow, you also want to run an external compiler such as ModelSim, XSim, or Riviera Pro. SVH’s external compiler integration enables you to run these automatically on file changes or at your request.

Learn more: usage

Learn more: file format

To get started, follow the steps below.

- Right-click a target—or the project—and click Automate Designflow > External Compiler

- Pick your desired external compiler

- Configure preferred options and press OK. A

tasks.jsonin the.vscodefolder is created - SVH instructs the external compiler to compile your target or project and repeats the process upon relevant file changes

- SVH populates the Problems view with the errors, warnings, and infos from the external compiler output. SVH also displays the problems on the code in the editor alongside Sigasi’s linting

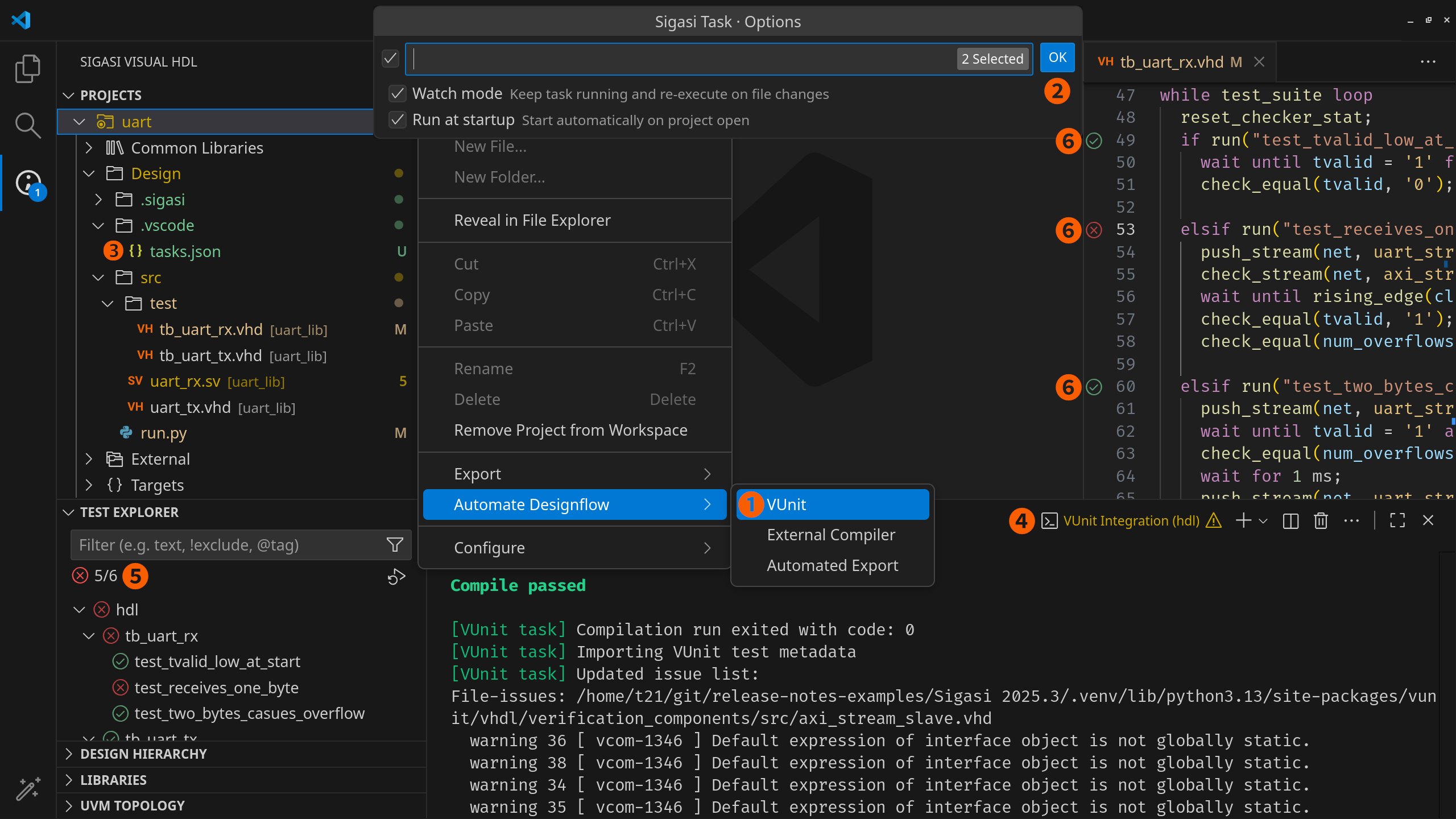

VUnit Integration

You can use SVH to automatically compile and run your VUnit testbench.

Learn more

To get started, follow the steps below.

- Right-click the project—or a target—and click Automate Designflow > VUnit

- Configure your preferred options and press OK

- A

tasks.jsonin the.vscodefolder is created - SVH instructs VUnit to compile your testbench files and repeats the process upon relevant file changes

- The Test Explorer is popular with VUnit test cases that you can run

- Upon running the tests, the results are shown in the editor

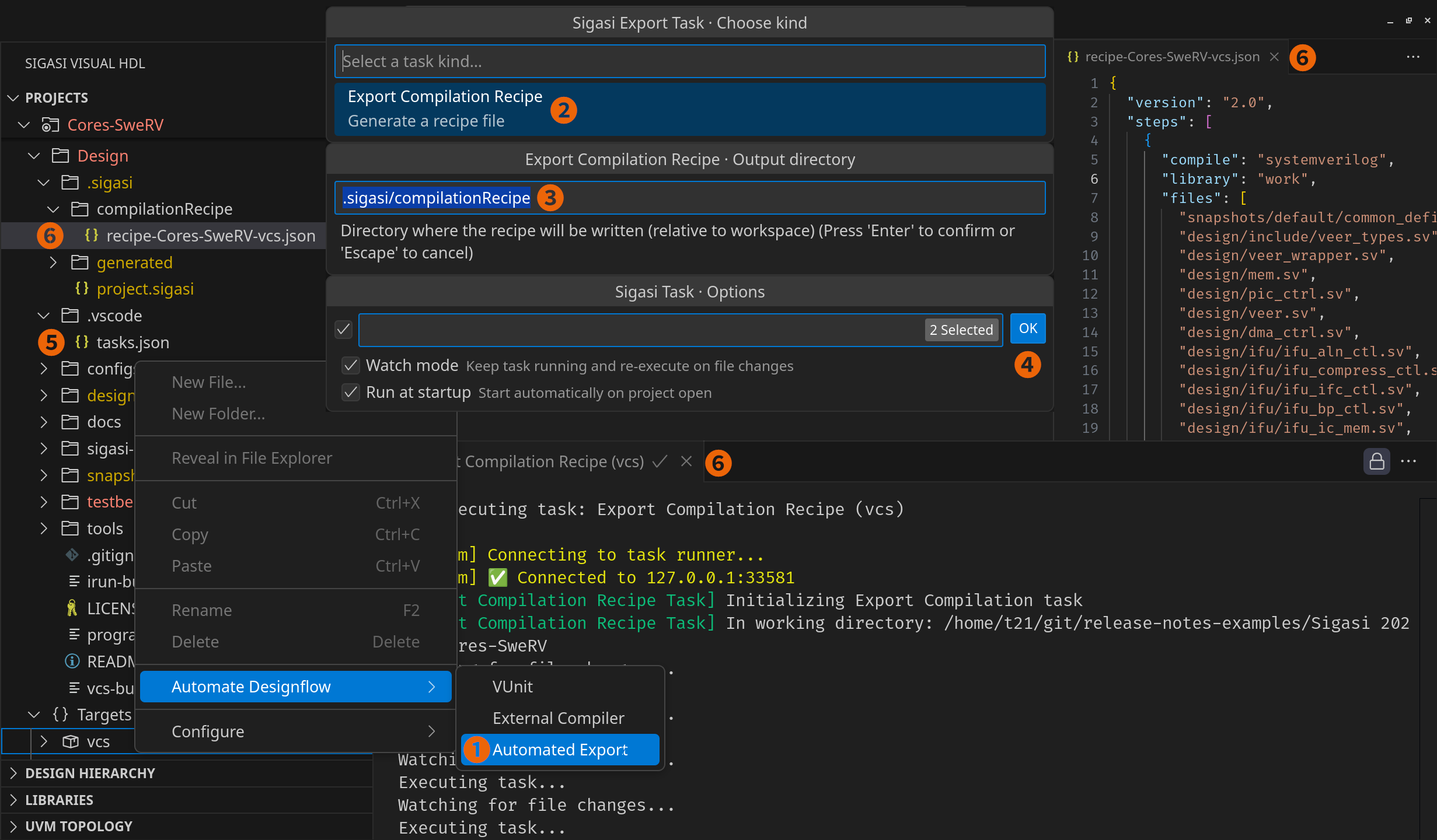

Compilation Recipe Generation

The Compilation Recipe introduced in the previous release received a facelift, making it even more powerful. It can now be automatically generated, making it easier than ever to drive downstream tools from SVH.

Learn more- Right-click a target—or the project—and click Automate Designflow > Automated Export

- Select the

Export Compilation Recipe - Configure where to save the compilation recipe

- Configure your preferred options and press OK

- A

tasks.jsonin the.vscodefolder is created - SVH generates a compilation recipe, ready to drive your downstream tools

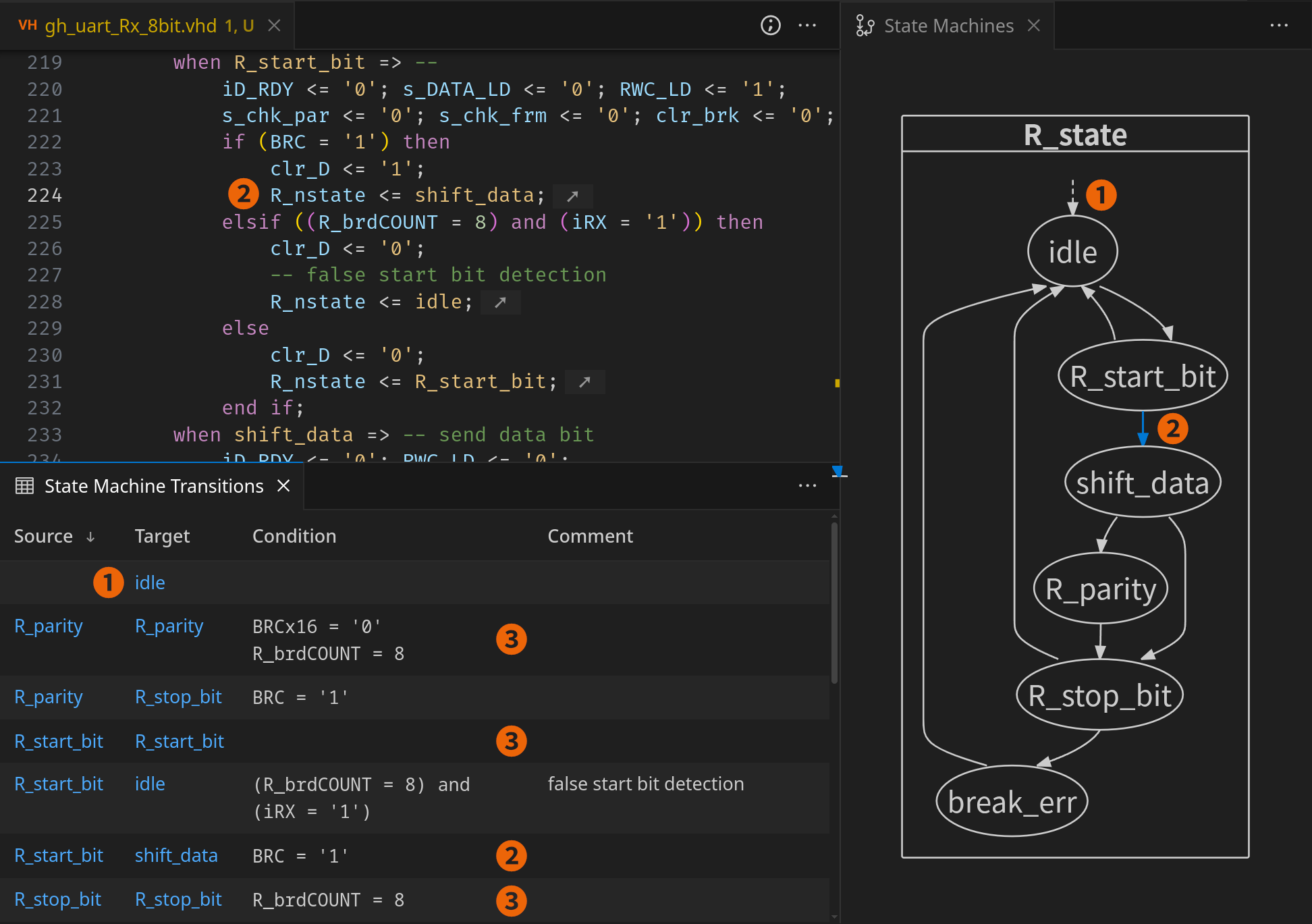

State Machine Transitions

Once state machines become large, it becomes difficult to visualize transition conditions and comments yet keep the diagram comprehensible. To assist you in those scenarios, there is now a State Machine Transitions table. It is available as a separate view, but it is also included in the Documentation View and generated documentation.

Learn more

You can open the table by clicking the Sigasi logo

- The reset state is always shown at the top

- Every transition is shown in the table. Clicking it highlights the transition in the diagram. Double-clicking highlights it in the code.

- Self-transitions are also shown in the table, but not in the diagram

Sigasi Projects (Preview ✨)

Sigasi projects are the future of projects for SVH. They are a more powerful version of the current Eclipse-compatible projects, allowing for:

- Easy integration with existing toolchains such as VCS and Questa

- Extensive reuse of existing IP

- Clean directory structure

- Compilation Recipe generation

- Maximum settings sharing within and between teams

If you are starting a new project with Sigasi, you should seriously consider using the new project format.

Keep in mind, though, that we are still collecting feedback and might make small changes in the future. To help you get started, do not hesitate to contact us .

While you are probably used to your project having the .project and .library_mapping.xml files and a .settings folder, the new Sigasi projects are configured through a project.sigasi JSON file and a .sigasi folder.

Learn more

To get started, create or import a project through the Sigasi: Create New Sigasi Project (Preview Feature) command.

If you have existing build scripts, follow the scripted steps. Otherwise, follow the manual steps.

Scripted

After running the creation command, the project.sigasi is opened. Remove the empty libraryMapping and instead add your build command and any required environment variables. For example:

{

"targets": {

"vlog": {

"environment": { "RV_ROOT" : "." },

"command": "make --always-make -f $RV_ROOT/tools/Makefile vlog"

}

}

}

That is it. Sigasi now knows all about your project and will remain in sync with your existing build scripts! You do not have to take our word for it. Sigasi projects are already in use in open-source projects such as UVVM , maximizing productivity through a simple one-liner.

Did you configure multiple tools or are you designing for multiple hardware platforms? Simply define multiple targets.

Are you reusing existing IP? Simply use target dependencies.

Learn more

Manual

If you are starting from scratch, there is no need to write any JSON files. Instead, simply right-click folders and files in the Design node to configure your project. You can Change Library or configure the Language Version. By right-clicking the Design node itself, you can configure dependencies and configure the Verilog Preprocessor and the VHDL Conditional Variables in the Target Settings page.

Learn more

Library Mapping Guidance

A project is made up of files that are mapped to libraries. To unlock Sigasi’s full potential, you have to ensure that your library mapping is set up correctly. That is why we added many hints to guide you during your project setup.

Sigasi CLI in SVH

This release makes the Sigasi CLI available in the VS Code terminal. While it still requires an Enterprise license, the license configured in VS Code will be reused. This convenient combo package of the extension and the CLI enables even simpler installs for your IT team. The standalone CLI is still available to deploy in your CI environment.

Quality of Life

- Simplified project creation dialog

- Do not show Code Lenses to open compilation log files for manual targets in Sigasi projects

- Added a button to the license settings in license error messages

- Use the same ordering strategy for the Libraries View and Projects View

- Enlarged the selectable region for the reset transition in the State Machines Diagram

- Replaced the modal dialog after documentation generation by a VS Code notification

- Added semantic highlighting tokens for

input,output, andinoutports - Enhanced the jumping to the Sigasi View to only open when a Sigasi project or Eclipse-compatible project is detected

- Verilog Added an expand all button to the Class Hierarchy

- Verilog Made the default mode for Class Hierarchy show both sub- and superclasses

- Verilog Removed the unused

Rule severity for RTLin theVerilog Errors/Warningssettings page - Verilog Added autocomplete for include files

- Verilog Added context menu item to remove a folder from the workspace

- Verilog Added a

Reveal in File Explorercontext menu item

Further New and Noteworthy

- Comments separated from by code by an empty line are now also associated with the element below it

- Allow setting library database directory to an empty folder

- Added state machine inlay hints for reset and

othersclauses - Improved error messaging for system errors during extension install

- Mark unused states as dead states (no outgoing transitions) when there are unresolved transitions

- Offer a context-based name when exporting diagrams

- Added an error for tasks and void function calls used in assignments or as parameters

- Moved the Talkback settings to

Userallowing to configure it for remote connections - Provided a backup unzipping methodology when

zstd-jniis unavailable - Hide

ieeeandstdin library mapping - Hide the

Project files overviewin the table of contents of the generated documentation when exporting with theNoneoption for diagrams - Improved the first-time experience regarding pop-ups and walkthroughs

- Show a pop-up when Community Edition is enabled and a commercial license is also configured

- Hide

Exclude from Buildfor unmapped files - Added a warning when a project has no library mapping

- Made Talkback setting available in both the

UserandRemotesettings - Verilog Improved highlighting for the “Register initialization” warning

- Verilog Added formatting for module instantiation parameters

- Verilog Added support for environment variables in include statements

- Verilog Added support for absolute paths in include statements

- Verilog Added support for binding VHDL entities using the Verilog bind construct

- VHDL Added a warning when using VHDL 2019 conditional processing on files configured with a VHDL version < 2019

- VHDL Expanded the incorrect assignment operator linting rule to check assigning to aggregates

- VHDL Added duplicate design unit validation for VHDL

Bug Fixes

- The

RESTORE DEFAULTSbutton on the Active Tools and Libraries page is now disabled if there are no tools or libraries to configure - Fixed missing state machine inlay hints

- Fixed error reporting for importing invalid Eclipse templates

- Fixed unexpected

Incomplete sensitivy listwarning - Fixed focusing of hidden windows using the

Show inaction - Fixed editing of the Library Database setting on remote hosts

- Fixed the documentation generation for paths using non-ASCII characters

- Fixed blank Library View on startup

- Verilog Fixed missing parameters in autocomplete

- Verilog Fixed missing refreshes for hidden UVM Diagrams

- Verilog Fixed hover actions in the Preprocessor view

- Verilog Fixed incorrect name in the Outline View for nested modules

- Verilog Fixed missing transition conditions in the State Machines Diagram

- Verilog Fixed the

APPLYbutton on settings pages remaining green even after applying - Verilog Fixed missing navigation to files with non-standard file extensions in include statements

- Verilog Added a warning when trying to assign a void function or task to a variable

- Verilog Fixed false positive errors when binding VHDL entities using the bind construct

- Verilog Ensured sorting is maintained when showing inherited members in the Class Hierarchy

- VHDL Fixed double tab characters in the

packageautocomplete - VHDL Fixed formatting alignment of types for subprogram parameters

- VHDL Fixed autocomplete in literals

- VHDL Fixed formatting alignment of comments when configured to column 0

- VHDL Fixed formatting alignment of multi-line package members

- VHDL Fixed formatting of trailing comments on the last line of a file

Talkback

- Added information regarding checked-out licenses

Updates

- Renamed the

Sigasi: Open Settingscommand toSigasi: Open Project Settings - Renamed the

Add Project...context menu item toCreate or Open Project... - Renamed the

New Tutorial Project...context menu item toCreate Tutorial Project... - Renamed the

New Demo Project...context menu item toCreate Demo Project... - Removed timestamp and Sigasi version in generated documentation by default. You can enable it again through an option in the UI or via the

--include-revisionand--include-versioncommand line options - Removed the

Enable experimental Sigasi project supportoption. You can now create a Sigasi project via the Sigasi: Create New Sigasi Project (Preview Feature) command. - Flipped the default for the

sigasi.trace.includePeriodicMessages Include Periodic Messagesto false - The Windows binary filename was updated to

sigasi-visual-hdl-windows-x.y.z.vsixfromsigasi-visual-hdl-win32.vsix - The Linux binary filename was updated to

sigasi-visual-hdl-linux-x.y.z.vsixfromsigasi-visual-hdl-linux.vsix - Updated the minimum VS Code version to 1.82.0, up from 1.80.0

Update or Install

If you have downloaded SVH from the VS Code Marketplace , your installation will automatically update.

You can also download the latest .vsix file and manually install it in VS Code.

- Linux: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-linux.vsix

- Windows: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-windows.vsix

The SHA sum is downloadable from https://download.sigasi.com/vs-code/updates/latest/vs-code-sha1.txt .

System Requirements

Sigasi Visual HDL requires:

- Windows 10 or Windows 11 64-bit

- 64-bit Red Hat Enterprise Linux RHEL 8 or higher

- VS Code >= 1.82 and < 2.0

We recommend having at least 8 GB of memory and about 1 GB of free disk space available for Sigasi Visual HDL.

Feedback

Our Support Team happily welcomes any of your feedback.

Transition Information

This is the final feature release for Sigasi Visual HDL in Eclipse. After a year of ramping down development on Eclipse, we highly recommend you to now transition to SVH in VS Code. Do not hesitate to contact us to help you with your transition.

Please check the final release notes for information specific to using SVH in Eclipse.